文章编号: 1001 - 9014(2016)02 - 0172 - 05

DOI: 10.11972/j. issn. 1001 - 9014. 2016. 02. 009

# Direct extraction method of equivalent circuit parameters for stacked transformer

CHENG Ran<sup>1,2</sup>, CHEN Bo<sup>1</sup>, LUO Dan-Ting<sup>1</sup>, GAOJian-Jun<sup>1,2</sup>

- (1. Shanghai Key Laboratory of Multidimensional Information Processing, School of Information Science and Technology, East China Normal University, Shanghai 200241, China;

- Shanghai Institute of Microsystem and Information Technology, State Key Laboratory of Transducer Technology, Shanghai 200050, China)

**Abstract:** A parameter-extraction approach for the stacked on-chip transformer, which combines the analytical approach and the empirical optimization procedure, was developed. The model parameters determined from the analytical expressions were considered as an initial guess of a subsequent optimization procedure leading to the final model parameters. Good agreement was obtained between simulated and measured results for a stacked transformer on silicon substrate in the frequency range  $100~\mathrm{MHz} \sim 60~\mathrm{GHz}$ .

Key words: parameter-extraction approach, equivalent circuit, stacked transformer

PACS: 85.30. De

## 片上叠层式变压器的建模及参数提取

程 冉1,2, 陈 波1, 骆丹婷1, 高建军1,2

- (1. 华东师范大学 信息科学技术学院 上海市多维度信息处理重点实验室,上海 200241;

- 2. 上海微系统与信息技术研究所 传感技术联合国家重点实验室,上海 200050)

摘要:结合分析法和优化法,针对片上叠层式变压器提出了一种参数提取方法.分析法得出的参数值作为优化法的初始值,从而得出最终的模型参数值.结果表明,在 $100~MHz\sim60~GHz$ 频率范围内,硅衬底的叠层式变压器S参数的仿真结果和测试结果吻合很好.

关键词:参数提取方法;等效电路;叠层式变压器

中图分类号:TN386.6 文献标识码:A

#### Introduction

Radio frequency integrated circuits (RFICs) such as low-noise amplifiers, voltage-controlled oscillators, mixers, and power amplifiers rely on a number of passive components including capacitors, varactors, resistors, inductors, transformers, and transmission lines. On-chip transformers are widely used to implement functions such as impedance conversion, resonant load, low-noise feedback, bandwidth enhancement, and differential-to-single conversion<sup>[1-7]</sup>.

Due to their multi-metal layer structures, on-chip transformers manufactured in RF-CMOS technology can have various structures. Since the amount of silicon area

occupied by transformers can be a limiting factor in most applications, interleaved or tapped structures are often replaced by stacked configurations, which offer higher magnetic coupling and area efficiency, albeit at the expense of increased parasitic capacitances<sup>[8-10]</sup>.

With the increase in demand of high-performance stacked transformers, accurate compact models are especially valuable for efficient simulation for RF circuit design. Because of the accuracy of the model is really dependent on the model parameters, an accurate procedure for extraction of the model parameters is extremely important for optimizing device performance of on-chip transformer based on silicon material system [11-13].

The model parameters can be obtained from S-parameters measurements by using numerical optimization

Received date: 2015 - 05 - 19, revised date: 2015 - 12 - 14

收稿日期:2015-05-19,修回日期:2015-12-14

Foundation items: Supported by National Natural Science Foundation of China (61474044)

Biography: CHENG Ran(1991-), female, master. Research area involves modeling of devices and circuits. E-mail; sqcrnupt@ sina.com

techniques. However, the accuracy of the numerical optimization methods that minimizes the difference between measured and modeled data can vary, depending on the optimization method and starting values, while the analytical methods allow us to extract the equivalent circuit model parameters in a straightforward manner [14-15].

The analysis and modeling of monolithic stacked transformers on silicon were addressed. This method is a combination of numerical optimization and direct extraction methods. It overcomes the drawbacks of both methods, while retaining their advantages. Section I describes the basic formalism of the new method used in the extraction procedure. In section II, extraction results are given and discussed. The conclusions are discussed in section

#### 1 Theoritical analysis

#### Equivalent circuit model

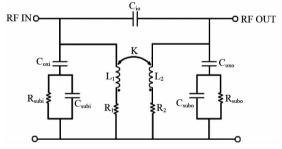

The dynamics of the stacked transformer can be captured in a compact model similar to the coupled inductors, as shown in Fig. 1, where  $C_{\rm oxi}$  and  $C_{\rm oxo}$  represent the oxide capacitances between the metal segments and Si substrate.  $C_{i0}$  represents the isolation capacitance between the input and output pad, and can be neglected because its small value (less than 1 fF normally) and does not affect the frequency response.  $C_{

m subi}$  ,  $C_{

m subo}$  and  $R_{

m subi}$  ,  $R_{

m subo}$  are the capacitances and resistances of the Si substrate, respectively.  $L_1$  is the inductance of primary alone and  $L_2$  is that of the secondary alone.  $R_1$  and  $R_2$  are the losses of primary and secondary, respectively. The parameter K, which represents the mutual inductance between the two wings, is related with the inductance  $L_1$ and  $L_2$ .

Fig. 1 Equivalent circuit model for stacked transformer 叠层式变压器的等效电路模型

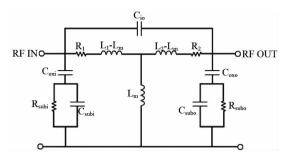

An alternative form of the equivalent circuit with an impedance inverter  $K=\frac{L_{\scriptscriptstyle m}}{\sqrt{L_{\scriptscriptstyle 1}L_{\scriptscriptstyle 2}}}$  can be used to represent the coupling, as shown in Fig. 2, where  $L_{\scriptscriptstyle m}$  indicates the

degree of coupling between primary and secondary. This equivalent circuit model can be divided into two parts. The outer part contains just pad parasitics, and the inner part contains intrinsic elementary cell.

#### Extraction of equivalent circuit parameters

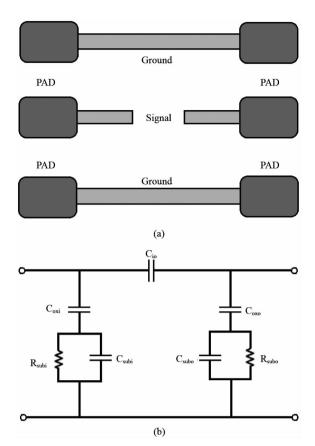

Figure 3 shows the open test structure layout with the corresponding equivalent circuit model. The short circuit Y-parameters of the equivalent circuit can be ex-

Fig. 2 Modified equivalent circuit model for stacked transformer

叠层式变压器的简化等效电路模型

pressed as the following:

$$Y_{11} = j\omega C_{io} + Y_{i}$$

, (1)

$Y_{22} = j\omega C_{io} + Y_{o}$  , (2)

$Y_{12} = Y_{21} = -j\omega C_{io}$  , (3)

$$Y_{22} = j\omega C_{i\alpha} + Y_{\alpha} \qquad , \qquad (2)$$

$$Y_{12} = Y_{21} = -j\omega C_{i0}$$

(3)

where

$$Y_i = \frac{1}{\frac{1}{i\omega C_{\text{out}}} + \frac{R_{\text{subi}}}{1 + i\omega R_{\text{out}} \cdot C_{\text{out}}}}, \quad (4)$$

$$Y_{i} = \frac{1}{\frac{1}{j\omega C_{\text{oxi}}} + \frac{R_{\text{subi}}}{1 + j\omega R_{\text{subi}} C_{\text{subi}}}} , \quad (4)$$

$$Y_{o} = \frac{1}{\frac{1}{j\omega C_{\text{oxo}}} + \frac{R_{\text{subo}}}{1 + j\omega R_{\text{subo}} C_{\text{subo}}}} . \quad (5)$$

and substrate resistances can be determined as follows:

$$C_{\text{oxi}} = -\frac{1}{\omega \text{Im} \left( \frac{1}{Y_{11}^o + Y_{12}^o} \right)}$$

, (6)

$$C_{\text{oxi}} = -\frac{1}{\omega \text{Im} \left( \frac{1}{Y_{11}^o + Y_{12}^o} \right)} , \quad (6)$$

$$C_{\text{oxo}} = -\frac{1}{\omega \text{Im} \left( \frac{1}{Y_{22}^o + Y_{12}^o} \right)} , \quad (7)$$

$$C_{io} = -\frac{\text{Im}(Y_{12}^o)}{\omega}$$

, (8)

$$C_{io} = -\frac{\text{Im}(Y_{12}^{o})}{\omega}, \quad (8)$$

$$R_{subi} = \text{Re}\left(\frac{1}{Y_{11}^{o} + Y_{12}^{o}}\right), \quad (9)$$

$$R_{\text{subo}} = \text{Re}\left(\frac{1}{Y_{22}^{o} + Y_{12}^{o}}\right)$$

(10)

In the high frequency ranges, the substrate capacitance (  $C_{

m subi}$  and  $C_{

m subo}$  ) can be determined from imaginary

parts of

$$1/(Y_{11}^o + Y_{12}^o)$$

and  $1/(Y_{22}^o + Y_{12}^o)$ :

$$C_{\text{subi}} = \frac{1}{\omega} \text{Im} \left\{ 1/\left[ \left( \frac{1}{Y_{11}^o + Y_{12}^o} \right) - \frac{1}{j\omega C_{\text{oxi}}} \right] \right\} , (11)$$

$$C_{\text{subo}} = \frac{1}{\omega} \text{Im} \left\{ 1/\left[ \left( \frac{1}{Y_{22}^o + Y_{12}^o} \right) - \frac{1}{j\omega C_{\text{oxo}}} \right] \right\}$$

$$. (12)$$

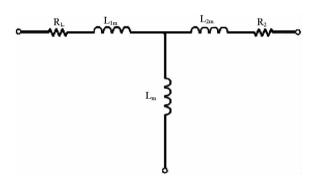

The superscript *o* denotes the open test structure. As shown in Fig. 4, after de-embedding parasitics, S-parameters are transformed to Z-parameters, the intrinsic elements can be determined directly as:

$$R_1 = \operatorname{Re}(z_{11}^i) \qquad , \quad (13)$$

$$R_2 = \operatorname{Re}(z_{22}^i) \qquad , \quad (14)$$

$$R_{2} = \text{Re}(z_{22}^{i}) , (14)$$

$$L_{1m} = \frac{\text{Im}(z_{11}^{i} - z_{12}^{i})}{\omega} , (15)$$

Fig. 3 (a) open test structure, (b) equivalent circuit model 图 3 (a) 开路测试结构, (b) 开路等效电路模型

Fig. 4 Transformer intrinsic cell 图 4 变压器本征单元

$$L_{2m} = \frac{\text{Im}(z_{22}^{i} - z_{12}^{i})}{\omega} , \quad (16)$$

$$L_{m} = \frac{\text{Im}(z_{12}^{i})}{\omega} . \quad (17)$$

The superscript i denotes the intrinsic structure.

This method also can be considered as an initial guess of a subsequent optimization procedure leading to the final model parameters.

The optimization error is defined by the RMS (Root Mean Square) error of S-parameters as error function criterion:

RMS target =

$$\sqrt{\frac{1}{N} \sum_{i=1}^{N} |S_{ij}^{m}|^{2}}$$

, (18)

RMS error =

$$\sqrt{\frac{1}{N} \sum_{i=1}^{N} \frac{|S_{ij}^{s} - S_{ij}^{m}|^{2}}{[\text{RMS target}]^{2}}}$$

, (19)

where the superscript m denotes the measured S-parameters, s denotes the simulated S-parameters.

#### 2 Results and discussions

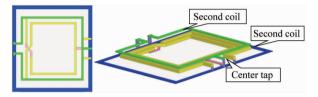

To illustrate the above model and parameter extraction method, we presented the extracted model parameters for the stacked on-chip transformer using IBM 130 nm 1P8M RF CMOS technology, as shown in Fig. 5.

Fig. 5 Structure of the stacked transformer 图 5 叠层式变压器结构

In this work, stacked transformer with one turn as primary coil on the first layer and two turns as secondary on another layer has been designed. The metal width is 3  $\mu m$  for both two coils, the thickness of primary is 1.325  $\mu m$  and the secondary one is 3.3  $\mu m$ . The gap between the two metals is 1.45  $\mu m$ . Open-loaded S-parameters were measured and de-embedded for the parasitics introduced by GSP PAD up to 60 GHz using an Agilent E8464A network analyzer.

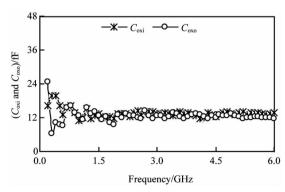

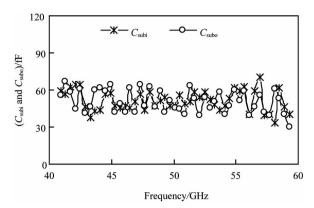

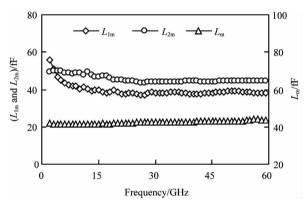

Figure 6 shows the initial extracted capacitances  $C_{\rm oxi}$  and  $C_{\rm oxo}$  in the low frequency range. Over a wide frequency range, the value variations are very small and almost negligible, and rather constant values are observed. It is noted that  $C_{\rm oxi}$  and  $C_{\rm oxo}$  are very close, because the test structure is symmetric. Figure 7 shows the initial extraction of substrate capacitance  $C_{\rm subi}$  and  $C_{\rm subo}$ . It is observed that the substrate capacitances at input and output ports are very close. Extracted results of inductances  $L_{\rm 1m}$ ,  $L_{\rm 2m}$  and  $L_{\rm m}$  are shown in Fig. 8. It is found that the values of  $L_{\rm 1m}$ ,  $L_{\rm 2m}$  and  $L_{\rm m}$  are independent of frequency from 1GHz to 60 GHz, in spite of slight slopes of the extracted  $L_{\rm 1m}$  and  $L_{\rm 2m}$  in the low frequency ranges.

Fig. 6 Extracted pad capacitances versus frequency 图 6 提取的 pad 电容随频率变化的曲线图

Fig. 7 Extracted substrate capacitances versus frequency 图 7 提取的衬底电容随频率变化的曲线图

Fig. 8 Extracted  $L_{\rm lm}$  ,  $L_{\rm 2m}$  and  $L_{\rm m}$  versus frequency 图 8 提取的线圈自感  $L_{\rm lm}$  、 $L_{\rm 2m}$  和互感  $L_{\rm m}$  随频率变化的曲线图

Table 1 summarizes the extracted model parameters using the analytical method mentioned above, and optimized values are given for comparison. The final values are very close to the analytical values.

Table1 Extracted and optimized values of model parameters 表 1 提取的模型参数值和优化的模型参数值

| Model parameters              | Extracted values | Optimized values |

|-------------------------------|------------------|------------------|

| $C_{\rm io}/{ m fF}$          | 0.06             | 0.06             |

| $C_{ m oxi}/{ m fF}$          | 13.4             | 13.5             |

| $C_{ m oxo}/{ m fF}$          | 13.2             | 13.0             |

| $C_{\rm subi}/{\rm fF}$       | 44               | 43               |

| $C_{ m subo}/{ m fF}$         | 49               | 50.1             |

| $R_{ m subi}\!/\Omega$        | 36               | 35               |

| $R_{ m subo}\!/\Omega$        | 35.5             | 35               |

| $L_{1\mathrm{m}}/\mathrm{pH}$ | 37.8             | 38               |

| $L_{\rm 2m}/{ m pH}$          | 43.7             | 44               |

| $L_{\it m}/{\rm pH}$          | 44.1             | 44               |

| $R_1/\Omega$                  | 1.44             | 1.45             |

| $R_2/\Omega$                  | 1.32             | 1.3              |

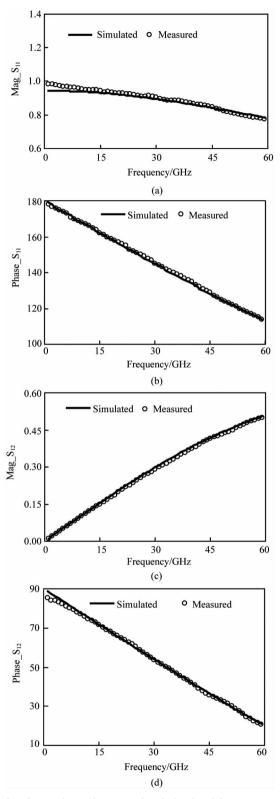

Figure 9 compares the magnitude and phase of measured and modeled S-parameters for the stacked transformer in the frequency range of  $100~MHz\sim60~GHz$ . The circle indicates the modeled values and the lines the measured ones. It is noted that there are slight

Fig. 9 Comparison of measured and simulated S-parameters of the stacked spiral transformer. (a) Magnitude of  $S_{11}$ , (b) phase of  $S_{11}$ , (c) magnitude of  $S_{12}$ , and (d) phase of  $S_{12}$  图 9 叠层式变压器的测量和仿真 S 参数比较图(a)  $S_{11}$ 的幅值随频率变化的曲线图,(b)  $S_{11}$ 的相位随频率变化的曲线

图,(c)  $S_{12}$ 的幅值随频率变化的曲线图,(d)  $S_{12}$ 的相位随频

率变化的曲线图

slopes of the modeled S-parameters against measured ones in low frequency. The modeled S-parameters agree very well with the measured S-parameters, validating the accuracy of the proposed model and parameter extraction method. Good agreement was obtained between simulated and measured results with a RMS error less than 5%. Therefore, the accuracy of the model is validated in the frequency range  $100~\mathrm{MHz} \sim 60~\mathrm{GHz}$ .

#### 3 Conclusion

A parameter-extraction approach for the stacked onchip transformer, which combines the analytical approach and the empirical optimization procedure was presented. The accuracy of the proposed method was validated by the excellent agreement between the simulated and measured results of the stacked spiral transformer using IBM 130 nm 1P8M RF CMOS technology in the frequency range 100 MHz ~ 60 GHz.

#### **Acknowledgements**

This work was supported in part by the National Natural Science Foundation of China under Grant 61474044, and Shanghai Minhang Excellent Talents.

### References

- Gao J. RF and microwave modeling and measurement techniques for field effect transistors [M]. Raleign, Scitech Publishing, Inc., NC, 2010

- [2] Bahll J, Griffin E L, Dilly J, etal. Low loss multilayer microstrip line for monolithic microwave integrated circuits applications [J]. Int J RF Microwave Comput Aided ENG, 1998, 8(6): 441-454.

- [3] Bahl I J. High current handling capacity multilayer inductors for RF and microwave circuits [ J ]. Int J RF Microwave ComputAided ENG,

- 2000, 10(2): 139 146.

- [4] Gao J, Yang C. Microwave modeling and parameter extraction method for multilayer on-chip inductors [J]. International Journal of RF and Microwave Computer-Aided Engineering, 2012, 23(3):343-348.

- [5] Yan N, Yang C, Gao J. An approach for determining equivalent circuit model of on-chip inductors [J]. Microwave and optical technology letters, 2013,55(10):2363-2370.

- [6] NiknejadA M, Meyer RG. Analysis, design, and optimization of spiral inductors and transformers for Si RF IC's [J]. IEEE J. Solid-StateCircuits, 1998, 33 (10):1470-1481.

- [7] Zhou J J, Allstot D J. Monolithic transformers and their applications and differential CMOS RF low-noise amplifier [J]. IEEE J. Solid-State Circuits, 1998, 32 (12): 2020 – 2027.

- [8] CassanD J, Long J R. A 1-V transformer-feedback low-noiseamplifier for 5-GHz wireless LAN in 0.18- \_m CMOS[J]. IEEE J. Solid-State Circuits, 2003, 38(3):427-435.

- [9] Long J R. Monolithic transformers for silicon RF IC design [J]. IEEEJ. Solid-State Circuits, 2000, 35(9):1368-1382.

- [10] Maligeorgos J P, Long J R. A low-voltage 5.1 5.8-GHz imagereject-receiver with wide dynamic range [J]. IEEE J. Solid-State Circuits, 2000, 35(12):1917-1926.

- [11] Zolfaghari A, Chan A, Razavi B. Stacked inductors and transformersin CMOS technology[J]. IEEE J. Solid-State Circuits, 2001, 36 (4): 620-628.

- [12] RejaeiK T Ng B, BurghartzJ N. Substrate effects in monolithic RF transformers on silicon [J]. IEEE Trans. Microw. Theory Tech., 2002, 50(1), 377-383.

- [13] Aokil, Kee S D, Rutledge D, et al. A 2.4-GHz, 2.2-W, 2 V fully-integrated CMOS circular-geometry active-transformer poweramplifier [C], "in Proc. IEEE Custom Integr. Circuits Conf., May 2001, 57 60.

- [14] KworkK, Luong H C. Ultra-low-voltage high-performanceCMOS VCOs using transformer feedback [J]. IEEE J. Solid State Circuits, 2005, 40 (3): 652-660.

- [15] Tiemeijer L F, Pijper R M T, Andrei C, et al. Analysis, design, modeling, and characterization of low-loss scalable on-chip transformers [J]. IEEE trasactionsonMicrowavetheoryandtechniques, 2013, 61 (7):2545-2557.