## Effect of extrinsic resistance on noise performance for deep submicron MOSFET

GAO Han-Qi, JIN Jing, ZHOU Jian-Jun\*

(School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University,

Shanghai 200240, China)

**Abstract:** This paper investigates the impact of extrinsic resistance on the noise performance of deep submicron MOSFETs (metal-oxide-semiconductor field-effect-transistor) using the noise correlation matrix method. Analytical closed-form expressions for calculating the four noise parameters are derived based on the small-signal and noise-equivalent circuit models. The results show strong agreement between simulated and experimental data for MOSFETs with a gate length of 40 nm and dimensions of  $4 \times 5 \mu\text{m}$  (number of gate fingers  $\times$  unit gate width).

**Key words:** equivalent circuits, MOSFET, parameter extraction, noise model, small signal model

## 外延电阻对深亚微米 MOSFET 噪声性能的影响

高涵祺, 金晶, 周健军\*

(上海交通大学 集成电路学院/信息与电子工程学院 模拟射频集成电路设计中心, 上海 200240)

**摘要:** 本文采用噪声相关矩阵法, 研究了外电路电阻对深亚微米 MOSFET 噪声性能的影响。基于小信号等效电路模型和噪声等效电路模型, 推导得到了四个噪声参数的解析闭合表达式。对于栅长 40 nm、尺寸为  $4 \times 5 \mu\text{m}$  (栅指数量  $\times$  单位栅宽) 的 MOSFET, 仿真结果与实验数据表现出良好的一致性。

**关 键 词:** 等效电路; CMOS; 参数提取; 噪声模型; 小信号模型

中图分类号: O43

文献标识码: A

## Introduction

While MOSFET modeling is well-established for digital and low-frequency analog applications, extending these models to high-frequency domains introduces significant challenges. At RF (radio frequency) frequencies, understanding and modeling thermal noise become critical, as it emerges as the dominant noise source in MOSFETs<sup>[1-3]</sup>. Analytical expressions for noise parameters are essential for optimizing the noise performance of MOSFETs used in low-noise amplifiers. These expressions offer valuable insights into the underlying physical mechanisms and enable an assessment of how various parameters in the small-signal equivalent circuit impact performance<sup>[4-5]</sup>.

However, modeling RF noise is complicated by its

sensitivity to parasitic and coupling effects associated with the gate, transmission lines, pads, and lossy substrates<sup>[6-11, 14-17]</sup>. For GaAs FETs, Fukui<sup>[9]</sup> proposed an empirical relationship between the noise figure and circuit parameters using fitting coefficients. Similarly, A. Cappy developed simplified analytical formulas for the minimum noise figure, noise conductance, and optimal source impedance, based on a fundamental equivalent circuit that accounts for intrinsic gate-to-source capacitance and extrinsic gate and drain resistance<sup>[10]</sup>.

This study introduces analytical formulas for the noise parameters of microwave MOSFETs, derived from a small-signal and noise-equivalent circuit model that incorporates the influence of extrinsic resistance. The paper is organized as follows: Section II details the noise-equivalent circuit model and the derivation of noise pa-

Received date: 2024-12-23, revised date: 2025-11-21

收稿日期: 2024-12-23, 修回日期: 2025-11-21

Foundation items: Supported by the National Key R&D Program of China (2020YFB1807301) and the National Natural Science Foundation of China (2024-MMT-07).

**Biography:** Gao Hanqi (2000-), male, Shanghai, PHD student. Research area involves mmW IC design. The authors are with the School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University. E-mail: gaohanqi@sjtu.edu.cn

\*Corresponding author: E-mail: zhujianjun@sjtu.edu.cn

parameter expressions. Section III presents experimental findings, and Section IV concludes the study.

## 1 Theory Analysis

### 1.1 Intrinsic equivalent circuit model

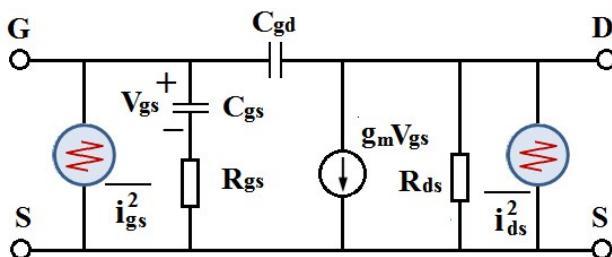

Fig. 1 depicts the intrinsic small-signal and PRC (Puel) noise-equivalent circuit model of the MOSFET. In this model,  $C_{gs}$  accounts for the combined gate-channel capacitance and gate-source overlap capacitance, while  $C_{gd}$  predominantly arises from the gate-drain overlap. The drain-to-source capacitance is represented by  $C_{ds}$ . Additionally, the transconductance is denoted by  $g_m$ , the drain conductance by  $g_{ds}$ , and  $\tau$  represents the time delay associated with the transconductance.

The gate-induced noise current  $\overline{i_g^2}$  and the drain-channel noise current  $\overline{i_{ds}^2}$  are represented by the following expressions<sup>[12]</sup>:

$$\overline{i_g^2} = 4kT\Delta f\omega^2 C_{gs}^2 R/g_m \quad , \quad (1)$$

$$\overline{i_{ds}^2} = 4kT\Delta f g_m P \quad , \quad (2)$$

The cross correlation between  $\overline{i_g^2}$  and  $\overline{i_{ds}^2}$  can be expressed as:

$$\overline{i_g^* i_{ds}} = C \sqrt{\overline{i_g^2} \overline{i_{ds}^2}} = 4kT\Delta f \omega C_{gs} C \sqrt{PR} \quad , \quad (3)$$

Here, R and P represent the gate and drain noise model parameters, respectively, while C denotes the correlation coefficient.

Based on the noise correlation matrix method<sup>[13]</sup>, the four noise parameters are derived as follows:

$$F_{\min} = 1 + 2k_2 + \frac{\omega C_{gs}}{g_m k_1} \sqrt{PR(1 - C^2)} \quad , \quad (4)$$

$$R_n = \frac{P}{g_m k_1} \quad , \quad (5)$$

Fig. 1 Intrinsic noise model of MOSFET

图1 MOSFET 本征噪声模型

$$G_{opt} = \omega C_{gs} \sqrt{\frac{R}{P} (1 - C^2)} \quad , \quad (6)$$

$$B_{opt} = -\omega [(C_{gs} + C_{gd}) - C \sqrt{\frac{R}{P} C_{gs}^2}] \quad , \quad (7)$$

where

$$k_1 = \frac{g_m + 2\omega^2 C_{gd} (\tau + C_{gs} R_{gs})}{g_m (1 + \omega^2 C_{gs}^2 R_{gs}^2)} \quad , \quad (8)$$

$$k_2 = \frac{\omega^2 C_{gs}}{g_m k_1} [P C_{gs} R_{gs} - C \sqrt{PR} (\frac{C_{gd}}{g_m} + C_{gs} R_{gs} + \tau)] \quad , \quad (9)$$

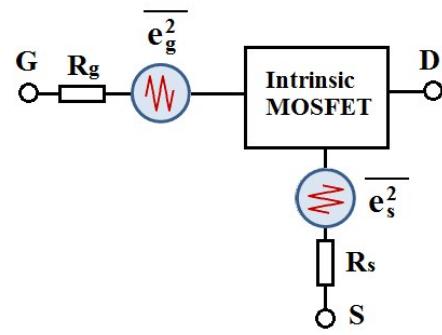

Fig. 2 Extrinsic resistance  $R_g$  and  $R_s$  noise model of MOSFET

图2 MOSFET 的外延电阻  $R_g$  和  $R_s$  噪声模型

Here,  $F_{\min}$  represents the minimum noise factor,  $R_n$  is the noise resistance,  $Y_{opt}$  is the optimum source admittance, while  $G_{opt}$  and  $B_{opt}$  denote the optimum source conductance and susceptance, respectively.

### 1.2 Intrinsic equivalent circuit model of effect of $R_g$ and $R_s$

The small-signal model incorporates three extrinsic resistances:  $R_g$ , which accounts for the distributed effects at the gate, and  $R_s$  and  $R_d$ , representing the source and drain resistances, respectively. These resistances are primarily influenced by the resistance of the lightly doped extensions of the source and drain diffusions. In the context of cascade noise figure calculations,  $R_g$  and  $R_s$  play crucial roles in determining the noise performance of the MOSFET, whereas the impact of  $R_d$  on noise performance is minimal and is typically negligible. Fig. 2 illustrates the noise model of the MOSFET, emphasizing the extrinsic resistances  $R_g$  and  $R_s$ .

The two noise sources,  $\overline{e_g^2}$  and  $\overline{e_s^2}$  represent the noisy behavior of the access resistances  $R_g$  and  $R_s$  and are expressed as:

$$\overline{e_i^2} = 4kT_o q R_i \Delta f (i = g, s) \quad , \quad (10)$$

where  $q$  is the electronic charge,  $k$  is Boltzmann's constant, and  $T_o$  is the ambient temperature.

The corresponding chain noise correlation matrix can be expressed as follows:

$$C_A^{INT} = 4kT \begin{bmatrix} R_n + R_g + R_s & \frac{F_{\min} - 1}{2} - R_n (Y_{opt})^* \\ \frac{F_{\min} - 1}{2} - R_n Y_{opt} & R_n |Y_{opt}|^2 \end{bmatrix} \quad , \quad (11)$$

Therefore, the four noise parameters are given by:

$$R_n^{INT} = R_n + R_s + R_g \quad , \quad (12)$$

$$B_{opt}^{INT} = \frac{R_n B_{opt}}{R_n^{INT}} \quad , \quad (13)$$

$$G_{opt}^{INT} = \sqrt{\frac{R_n}{R_n^{INT}} (G_{opt})^2 + \frac{R_n R_g B_{opt}^2}{(R_n^{INT})^2}} \quad , \quad (14)$$

$$F_{\min}^{INT} = F_{\min} + 2(R_n^{INT} R_{opt}^{INT} - R_n G_{opt}) \quad , \quad (15)$$

When take no account of  $C_{gd}$  and  $g_{ds}$ , the above expressions are simplified as:

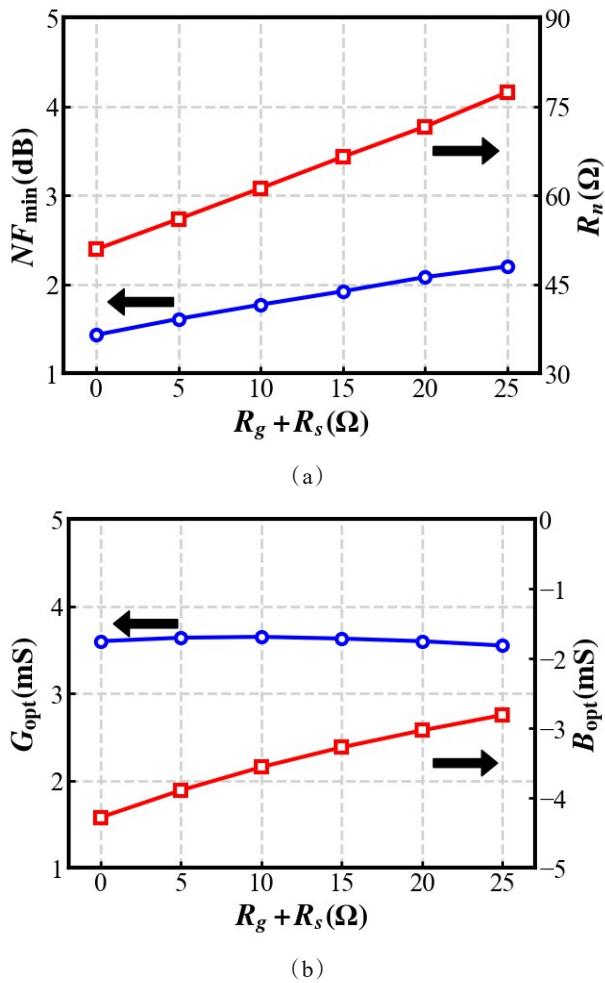

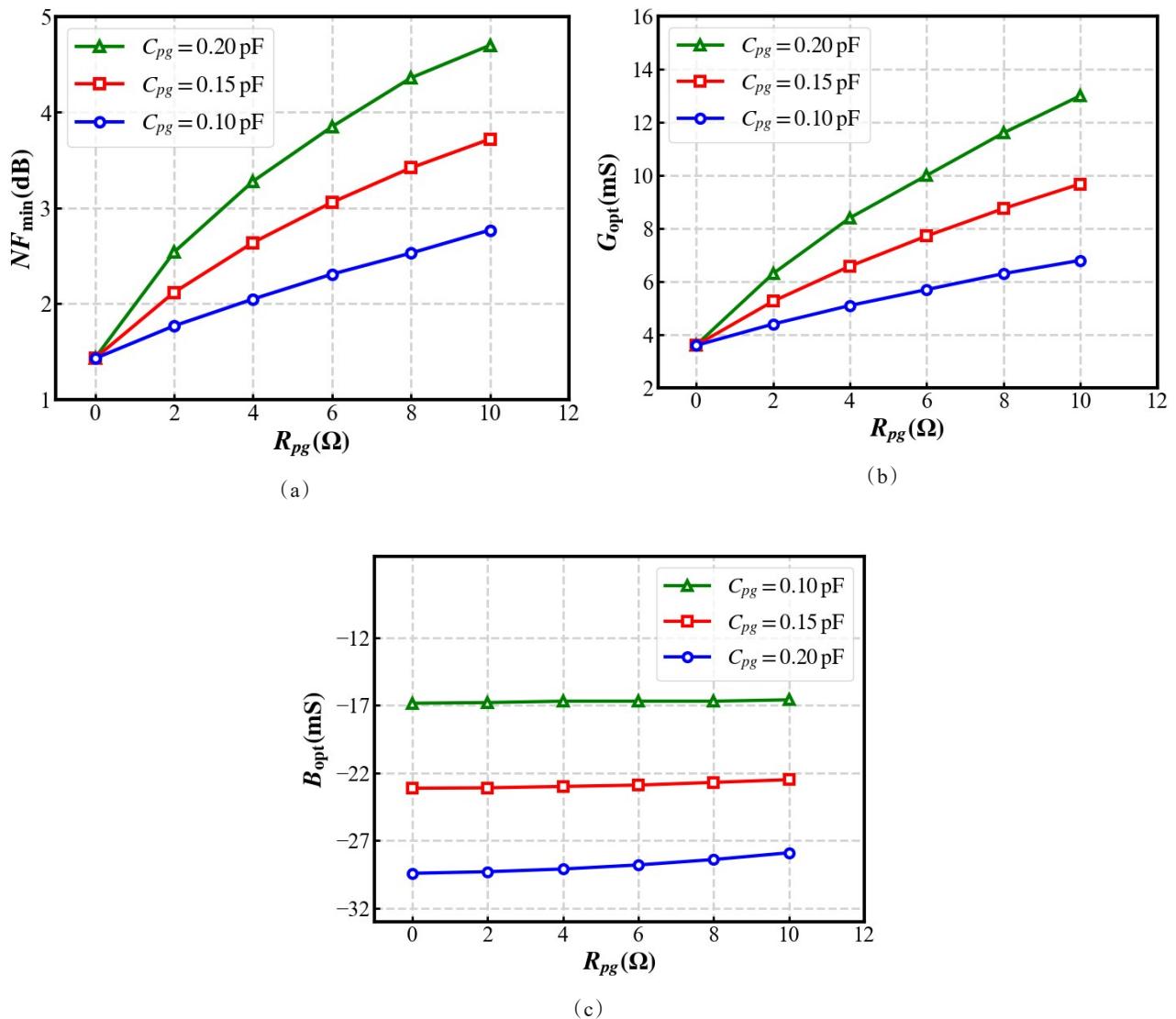

Fig.3 Noise parameters versus the sum of  $R_g$  and  $R_s$  (a)  $NF_{min}$  and  $R_n$  (b)  $G_{opt}$  and  $B_{opt}$

图3 噪声参数随  $R_g$  和  $R_s$  之和的变化关系(a)  $NF_{min}$  和  $R_n$  (b)  $G_{opt}$  和  $B_{opt}$

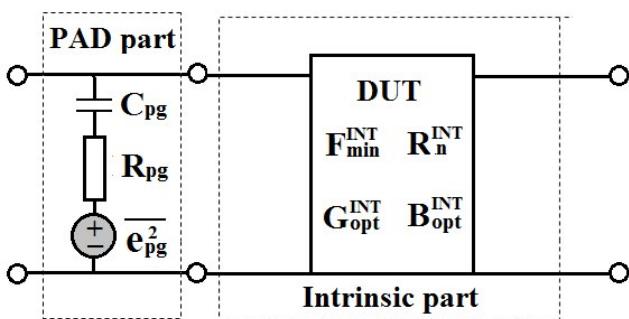

Fig.4 Substrate resistance  $R_{pg}$  noise model of MOSFET

图4 MOSFET 的衬底电阻  $R_{pg}$  噪声模型

$$R_n = \frac{P}{g_m} + R_g + R_s \quad , \quad (16)$$

$$C_A^t = 4kT \left[ \begin{array}{c} R_n^{INT} \\ \frac{F_{min}^{INT} - 1}{2} - R_n^{INT}(Y_{opt}^{INT} - M)^* \\ R_n^{INT}(|Y_{opt}^{INT}|^2 + |M|^2) \end{array} \right] \quad , \quad (26)$$

$$B_{opt} = -\omega C_{gs} \frac{(P - C \sqrt{PR})}{P + (R_g + R_s)g_m} \quad , \quad (17)$$

$$G_{opt} = \omega C_{gs} \frac{\sqrt{(R_g + R_s)g_m(P + R - 2C \sqrt{PR}) + PR(1 - C^2)}}{P + (R_g + R_s)g_m} \quad , \quad (18)$$

$$F_{min} = 1 + \frac{2\omega C_{gs}}{g_m} \sqrt{(R_g + R_s)g_m(P + R - 2C \sqrt{PR}) + PR(1 - C^2)} \quad , \quad (19)$$

Fig. 3 shows the noise parameters as a function of the sum  $(R_g + R_s)$ . It can be observed that the minimum noise figure  $NF_{min}$  and the equivalent noise resistance  $R_n$  increase as  $(R_g + R_s)$  increases. The optimum source conductance  $G_{opt}$  remains roughly independent of  $(R_g + R_s)$ , while the absolute value of the optimum source susceptibility  $B_{opt}$  decreases with an increase in  $(R_g + R_s)$ .

### 1.3 PAD parasitic

Fig. 4 illustrates the substrate resistance  $R_{pg}$  noise model of the MOSFET. It can be seen that the pad parasitic consist of two elements:  $R_{pg}$  and  $C_{pg}$ . The parasitic associated with the pad due to substrate losses are represented by the capacitor  $C_{pg}$  in series with the resistor  $R_{pg}$ .

For shunt RC network (as shown in Fig. 4), the signal parameters can be expressed as follows:

$$A_{PAD} = \begin{bmatrix} 1 & 0 \\ M & 1 \end{bmatrix} \quad , \quad (20)$$

with

$$M = \frac{j\omega C_{pg}}{1 + j\omega R_{pg} C_{pg}} \quad , \quad (21)$$

It should be noted that the correlation noise matrices for series and shunt RC networks are non-zero because the two-port networks are passive and lossy.

$$C_Z^{PAD} = 4kT \text{Re} [Z_{PAD}] = 4kT R_{pg} \begin{bmatrix} 1 & 1 \\ 1 & 1 \end{bmatrix} \quad , \quad (22)$$

$$C_A^{PAD} = 4kT \begin{bmatrix} 0 & 0 \\ 0 & N \end{bmatrix} \quad , \quad (23)$$

with

$$N = \frac{R_{pg}}{R_{pg}^2 + 1/(\omega C)^2} \quad , \quad (24)$$

In noise analysis applications involving the interconnection of two two-port networks, whether in cascade or otherwise, the resulting correlation matrix is related to the correlation matrices of the original two-port networks by<sup>[13]</sup>:

$$C_A^t = C_A^{PAD} + A_{PAD} C_A^{INT} A_{PAD}^+ \quad , \quad (25)$$

It should be noted that a more complex relationship is obtained for the cascading connection of networks, which also includes the chain matrix  $A_{PAD}$  of the first two-port.

$$\left[ \begin{array}{c} \frac{F_{min}^{INT} - 1}{2} - R_n^{INT}(Y_{opt}^{INT} - M)^* \\ R_n^{INT}(|Y_{opt}^{INT}|^2 + |M|^2) \end{array} \right] \quad , \quad (26)$$

The corresponding correlation noise matrix in impedance representation can be expressed as follows:

$$R_n^{PAD} = R_n^{INT} \quad , \quad (27)$$

$$B_{opt}^{PAD} = B_{opt}^{INT} - \frac{\omega C_{pg}}{1 + (\omega R_{pg} C_{pg})^2} \quad , \quad (28)$$

$$G_{opt}^{PAD} = \sqrt{(G_{opt}^{INT})^2 + K \left( \frac{F_{min}^{INT}}{R_n^{INT}} - 2G_{opt}^{INT} + K \right)} \quad , \quad (29)$$

$$F_{min}^{PAD} = F_{min}^{INT} + 2R_n^{INT} (K + G_{opt}^{PAD} - G_{opt}^{INT}) \quad , \quad (30)$$

with

$$K = \frac{R_{pg} (\omega C_{pg})^2}{1 + (\omega R_{pg} C_{pg})^2} \quad , \quad (31)$$

From Eq. (27), it is evident that the equivalent noise resistance is independent of the pad parasitic. Fig. 5 shows the three noise parameters as a function of

$R_{pg}$  and  $C_{pg}$ . It can be observed that the minimum noise figure  $NF_{min}$  increases with an increase in  $R_{pg}$  and  $C_{pg}$ , with a more significant effect observed for the pad capacitance  $C_{pg}$ . The optimum source conductance  $G_{opt}$  also increases with an increase in  $R_{pg}$  and  $C_{pg}$ . The optimum source susceptance  $B_{opt}$  remains independent of  $R_{pg}$  but increases with an increase in  $C_{pg}$ .

## 2 Experimental Verification

To validate the derived expressions for the extrinsic resistances, measurements were conducted on a  $4 \times 5 \mu\text{m}$  (number of gate fingers  $\times$  unit gate width) NMOSFET with a 40 nm gate length, up to a frequency of 40 GHz for S-parameter characterization. High-frequency noise parameter measurements were performed on-wafer over the 8-26 GHz range using an ATN microwave noise measurement system.

Fig.5 Noise parameters versus  $R_{pg}$  (a)  $NF_{min}$  (b)  $G_{opt}$  (c)  $B_{opt}$

图5 噪声参数随  $R_{pg}$  (a)  $NF_{min}$  (b)  $G_{opt}$  (c)  $B_{opt}$  变化图

**Table 1 The MOSFET parasitic parameters**

**表1 MOSFET 寄生参数**

| Parameters | Values | Units    | Parameters | values | Units    |

|------------|--------|----------|------------|--------|----------|

| $C_{pg}$   | 230    | fF       | $R_g$      | 30     | $\Omega$ |

| $C_{pd}$   | 230    | fF       | $R_d$      | 5      | $\Omega$ |

| $C_{pgd}$  | 2      | fF       | $R_s$      | 7      | $\Omega$ |

| $R_{pg}$   | 4      | $\Omega$ | $R_{pd}$   | 4      | $\Omega$ |

**Table 2 Intrinsic parameters ( $V_{ds}=1.2$  V)**

**表2 本征参数(漏源电压  $V_{ds}=1.2$  V)**

| Parameters    | Values | Parameters            | Values |

|---------------|--------|-----------------------|--------|

| $C_{gs}$ (fF) | 55     | $C_{gd}$ (fF)         | 10     |

| $C_{ds}$ (fF) | 25     | $R_{gs}$ ( $\Omega$ ) | 15     |

| $g_m$ (mS)    | 54     | $g_{ds}$ (mS)         | 10     |

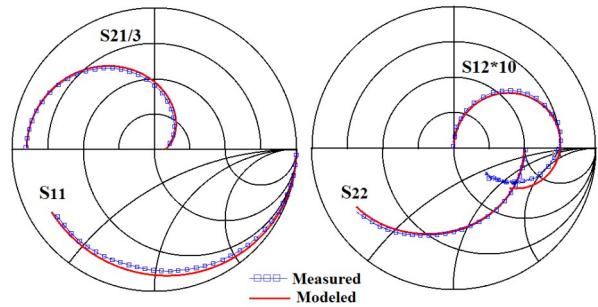

Fig. 6 Comparison of modeled and measured S parameters for the  $4 \times 5 \mu\text{m}$  MOSFET. Bias:  $V_{gs}=1.2$  V,  $V_{ds}=1.2$  V

图6  $4 \times 5 \mu\text{m}$  MOSFET建模S参数和测试S参数对比. 偏置条件:  $V_{gs}=1.2$  V,  $V_{ds}=1.2$  V

(a)

(b)

(c)

(d)

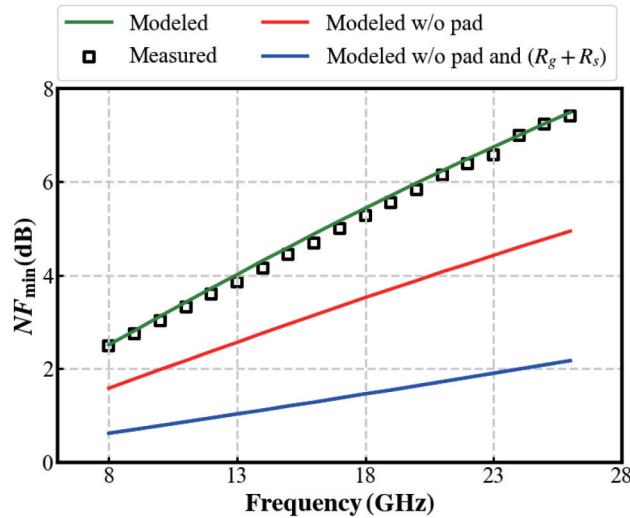

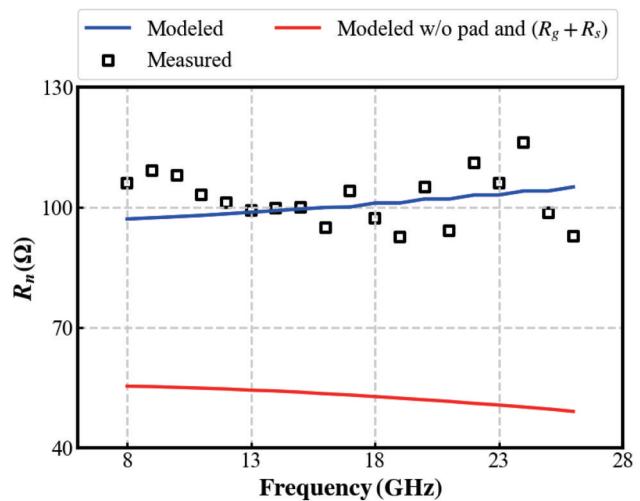

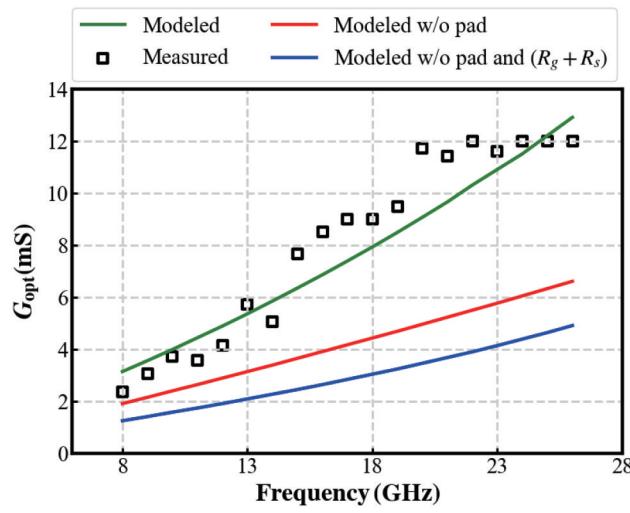

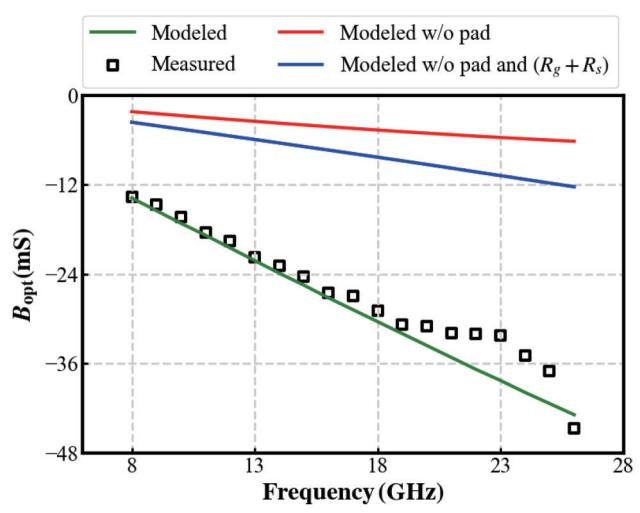

Fig. 7 Comparison of measured and modeled noise parameters for the  $4 \times 5 \mu\text{m}$  MOSFET. Bias:  $V_{gs}=1.2$  V,  $V_{ds}=1.2$  V (a)  $NF_{min}$  (b)  $R_n$

(c)  $G_{opt}$  (d)  $B_{opt}$

图7  $4 \times 5 \mu\text{m}$  MOSFET建模S参数和测试S参数对比. 偏置条件:  $V_{gs}=1.2$  V,  $V_{ds}=1.2$  V (a)  $NF_{min}$  (b)  $R_n$  (c)  $G_{opt}$  (d)  $B_{opt}$

## 2.1 PAD parasitic

Table 1 presents the MOSFET parasitic parameters, while Table 2 summarizes the extracted values of the small-signal elements at a constant drain-source voltage  $V_{DS} = 1.2V$ . Fig. 3 compares the measured and modeled S-parameters for the  $4 \times 5 \mu\text{m}$  MOSFET across the frequency range of 1 GHz to 40 GHz. The modeled S-parameters show excellent agreement with the measured data, validating the accuracy of the model.

## 2.2 Noise model verification

Fig. 6 shows the comparison between the measured and modeled noise parameters for the  $4 \times 5 \mu\text{m}$  MOSFET under the bias conditions  $V_{GS} = 1.2V$  and  $V_{DS} = 1.2V$ , demonstrating excellent agreement across the entire frequency range.

Fig. 7 presents a comparison of measured and simulated noise parameters, confirming the validity of the proposed method through strong agreement. As shown in Fig. 7(a), the influence of the pad and the combined resistances  $R_g$  and  $R_s$  on the minimum noise figure  $NF_{min}$  is evident. To minimize  $NF_{min}$ , it is crucial to keep  $R_g$  and  $R_s$  as low as possible. In Fig. 7(b), it can be seen that the equivalent noise resistance  $R_n$  is affected by  $R_g$  and  $R_s$ . Fig. 7(c) shows that the impact of  $R_g$  and  $R_s$  on the optimum source conductance  $G_{opt}$  is minimal. Lastly, due to the large pad capacitance  $C_{pg}$  (exceeding 200 fF), the effect of  $C_{pg}$  on the optimum source susceptance  $B_{opt}$  is significant, as illustrated in Fig. 7(d).

## 3 Conclusion

This paper introduces an approach for analyzing the impact of extrinsic resistances on the noise performance of deep submicron MOSFETs. Analytical expressions for the noise parameters of microwave MOSFETs are derived using a small-signal and noise equivalent circuit model that incorporates the effects of extrinsic resistances. Excellent agreement is achieved between simulated and measured results up to 26 GHz for  $4 \times 5 \mu\text{m}$  (number of gate fingers  $\times$  unit gate width) MOSFETs with a 40 nm gate length.

## References

- [1] POSPIESZALSKI M W. Interpreting transistor noise[J]. IEEE Microwave Magazine, 2010, 11(6): 61-69.

- [2] CHENG Y, DEEN M J, CHEN C H. MOSFET modeling for RF IC design[J]. IEEE Transactions on Electron Devices, 2005, 52(7): 1286-1303.

- [3] GAO J. Direct parameter-extraction method for MOSFET noise model from microwave noise figure measurement[J]. Solid-State Electronics, 2011, 63(1): 42-48.

- [4] GAO H, JIN J, ZHOU J. An approach to determine noise model parameter for submicron MOSFET from RF noise figure measurement[J]. IEEE Journal of the Electron Devices Society, 2024, 12: 692-697.

- [5] WANG S C, CHEN K M, LIAO K H, et al. Comprehensive noise characterization and modeling for 65-nm MOSFETs for millimeter-wave applications[J]. IEEE Transactions on Microwave Theory and Techniques, 2010, 58(4): 740-746.

- [6] GAO J, WERTHOFF A. Scalable small signal and noise modeling for deep submicron MOSFETs[J]. IEEE Transactions on Microwave Theory and Techniques, 2009, 57(4): 737-744.

- [7] GUO J C, LIN Y M. A new lossy substrate de-embedding method for sub-100 nm RF CMOS noise extraction and modeling[J]. IEEE Transactions on Electron Devices, 2006, 53(2): 339-347.

- [8] ZHANG H, NIU G, LIANG Q, et al. Extraction of drain current thermal noise in a 28 nm high-k/metal gate RF CMOS technology[J]. IEEE Transactions on Electron Devices, 2018, 65(6): 2393-2399.

- [9] FUKUI H. Design of microwave GaAs MESFET's for broadband low-noise amplifier[J]. IEEE Transactions on Microwave Theory and Techniques, 1979, 27(7): 643-650.

- [10] CAPPY A. Noise modeling and measurements techniques[J]. IEEE Transactions on Microwave Theory and Techniques, 1988, 36(1): 1-10.

- [11] ASGARAN S, DEEN M J, CHEN C H, et al. Analytical determination of MOSFET's high-frequency noise parameters from NF50 measurements and its application in RFIC design[J]. IEEE Journal of Solid-State Circuits, 2007, 42(5): 1034-1043.

- [12] PUCEL R A, HAUS H A, STATZ H. Signal and noise properties of GaAs microwave FET[M]//MORTON L. Advances in Electronics and Electron Physics. New York: Academic Press, 1975: 35-98.

- [13] HILLBRAND H, RUSSER P H. An efficient method for computer-aided noise analysis of linear amplifier networks[J]. IEEE Transactions on Circuits and Systems, 1976, 23(4): 235-238.

- [14] PANDA D K, LENKA T R. Investigation of gate induced noise in E-mode GaN MOS-HEMT and its effect on noise parameters[J]. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, 2018, 31(5): e2318.

- [15] JENA B, DASH S, MISHRA G P. Effect of underlap length variation on DC/RF performance of dual material cylindrical MOS[J]. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, 2017, 30(5): e2175.

- [16] BANERJEE S, GHOSH M, MONDAL P, et al. Third order inverse multifunction filter employing MOS resistors and capacitors[J]. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, 2022, 35(5): e3002.

- [17] VISWANATHAN S, PRAVIN C, ARASAMUDI R B, et al. Influence of interface trap distributions over the device characteristics of AlGaN/GaN/AlInN MOS-HEMT using Cubic Spline Interpolation technique[J]. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, 2022, 35(1): e2936.