文章编号: 1001-9014(2024)03-0331-05

DOI: 10. 11972/j. issn. 1001-9014. 2024. 03. 006

# InGaAs/InAlAs InP-based HEMT with the current cutoff frequency of 441 GHz

$FENG~Rui-Ze^{1,2},~~CAO~Shu-Rui^{1,2},~~FENG~Zhi-Yu^{1,2},~~ZHOU~Fu-Gui^{1,2},~~LIU~Tong^1,\\ SU~Yong-Bo^{1,2},~~JIN~Zhi^{1,2*}$

- (1. High-Frequency High-Voltage Device and Integrated Circuits Center, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China;

- 2. School of Integrated Circuits, University of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract:** In this letter, an  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  InP-based HEMT with  $f_T > 400$  GHz was designed and fabricated successfully. A narrow gate recess technology was used to optimize the parasitic resistances. The gate length is 54.4 nm, and the gate width is  $2 \times 50~\mu m$ . The maximum drain current  $I_{DS.\,max}$  is 957 mA/mm, and the maximum transconductance  $g_{m.\,max}$  is 1 265 mS/mm. The current gain cutoff frequency  $f_T$  is as high as 441 GHz and the maximum oscillation frequency  $f_{max}$  reaches 299 GHz, even at a relatively small value of  $V_{DS} = 0.7~V$ . The reported device can be applied to terahertz monolithic integrated amplifiers and other circuits.

**Key words:** InP HEMTs, InGaAs/InAlAs, current gain cutoff frequency  $(f_T)$ , maximum oscillation frequency  $(f_{max})$ , gate recess

# 电流增益截止频率为441 GHz的InGaAs/InAlAs InP HEMT

封瑞泽<sup>1,2</sup>, 曹书睿<sup>1,2</sup>, 冯识谕<sup>1,2</sup>, 周福贵<sup>1,2</sup>, 刘 同<sup>1</sup>, 苏永波<sup>1,2</sup>, 金 智<sup>1,2\*</sup> (1. 中国科学院微电子研究所,高频高压器件与集成电路研究中心,北京100029; 2. 中国科学院大学集成电路学院,北京100049)

**摘要:**本文设计并制作了 $f_r > 400$  GHz 的  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  铟磷高电子迁移率晶体管(InP HEMT)。采用 窄栅槽技术优化了寄生电阻。器件栅长为54.4 nm, 栅宽为2×50  $\mu$ m。最大漏极电流  $I_{DS,max}$ 为957 mA/mm, 最大跨导 $g_{m,max}$ 为1265 mS/mm。即使在相对较小的 $V_{DS} = 0.7$  V下,电流增益截止频率 $f_r$ 达到了441 GHz,最大振荡频率 $f_{mx}$ 达到了299 GHz。该器件可应用于太赫兹单片集成放大器和其他电路中。

**关 键 词:** 铟磷高电子迁移率晶体管(InP HEMTs); InGaAs/InAlAs; 电流增益截止频率 $(f_r)$ ; 最大振荡频率 $(f_{max})$ ; 栅槽

中图分类号:TN385

文献标识码:A

#### Introduction

The InP based terahertz monolithic integrated circuit (TMIC) have potentials for applications in plenty of fields, such as high-resolution security imaging systems<sup>[1]</sup>, revolutionary communication networks<sup>[2]</sup>, and radio astronomy<sup>[3]</sup>. InP-based InGaAs/InAlAs HEMTs have demonstrated high operating frequency, low noise, high-gain performance, as well as good radiation resistance<sup>[4]</sup>, making them an important device for InP based TMIC.

In recent years, the requirements for higher opera-

tion frequency and larger output power of TMIC result in a strong push of THz transistor technologies with current gain cutoff frequency  $(f_T)$  and maximum oscillation frequency  $(f_{\max})$ . The operating frequencies of integrated circuit amplifiers have seen corresponding increase to as high as 1 THz, with InP HEMTs reaching 1.5 THz  $f_{\max}$  and 610 GHz  $f_T^{[5]}$ . And the recent literature reported the current record of  $f_T = 738$  GHz with a gate length of 19 nm<sup>[6]</sup>. Various efforts have been made to improve the  $f_T$  of InP based HEMTs, such as reducing the gate length  $(L_g)^{[7]}$ , source-to-drain spacing  $(L_{\rm SD})^{[8]}$ , and gate-to-channel dis-

Received date: 2023-04-13, revised date: 2023-05-26 收稿日期: 2023-04-13, 修回日期: 2023-05-26

Foundation item: Supported by The National Natural Science Foundation of China (61434006)

Biography: Feng Ruize (1995. 12-), male, Shanxi China, Ph. D. Research area involves InP HEMT and MMIC. E-mail: 13161075953@163. com

<sup>\*</sup>Corresponding author: E-mail: jinzhi@ime. ac. cn

tance  $(t_{\rm ins})^{[9]}$ , as well as optimizing the channel layer and the gate recess All the above measures are for minimizing the parasitic resistances, capacitances and increasing the transconductance.

In this letter, a narrow gate recess technology was used to optimize the parasitic resistances of InP based HEMTs. The  $\rm In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  HEMTs with gate length of 54. 4 nm were fabricated. The values of  $f_T$  and  $f_{\rm max}$  are as high as 441 GHz and 299 GHz, the maximum drain current  $I_{\rm DS.\,max}$  is 957 mA/mm, and the maximum transconductance  $g_{\rm m.\,max}$  is 1265 mS/mm. The InP based HEMTs with such high performances can be applied to terahertz monolithic integrated (TMIC) amplifiers and other circuits.

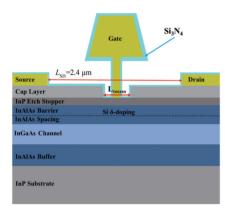

Fig. 1 A schematic cross-section of InP-based HEMT 图 1 InP HEMT 的截面示意图

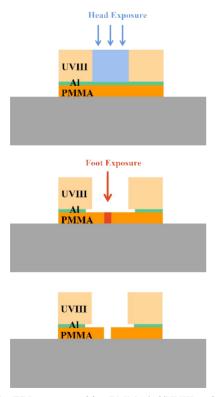

Fig. 2 The EBL process with a PMMA/Al/UVIII resist stack 图 2 PMMA/Al/UVIII 光刻胶堆叠的电子束光刻工艺

## 1 Experiment

The Schematic cross-section of InP-based HEMTs is shown in Fig. 1. The epitaxial layers of the devices were grown by gas source molecular beam epitaxy (GSMBE) on 3 inch semi-insulating InP (100) substrates. From bottom to top, the layers consists of a 500-nm In<sub>0.52</sub>Al<sub>0.48</sub>As buffer layer, a 10-nm In<sub>0.53</sub>Ga<sub>0.47</sub>As channel layer, a 3-nm unstrained In<sub>0.52</sub>Al<sub>0.48</sub>As spacer layer, Si delta doping layer with  $5\times10^{12}$  cm<sup>-2</sup> doping concentration, a 8-nm unstrained In<sub>0.52</sub>Al<sub>0.48</sub>As Schottky barrier layer, a 4-nm InP etch-stop layer for preventing over etching and a 40-nm multi-layer cap layer that combines heavily-droped In<sub>0.52</sub>Al<sub>0.48</sub>As/In<sub>0.53</sub>Ga<sub>0.47</sub>As and a heavily-droped In<sub>0.65</sub>Ga<sub>0.35</sub>As upper cap layer. Hall measurements from a Hall calibration epitaxial layer structure were made at room temperature, showing a carrier mobility of over  $10\,000\,\text{cm}^2/(\text{Vs})$ .

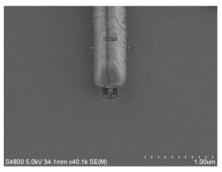

Fig. 3  $\,$  SEM photograph of the T-Gate and gate recess of the In-GaAs/InAlAs HEMT

图 3 InGaAs/InAlAs HEMT 的 T型栅和栅槽的 SEM 照片

The fabrication process of InP HEMTs mainly contains five steps, including mesa isolation, ohmic contact formation, gate recesses, T-Gates, and connection pads, which is similar to our previously reported devices [13]. Isolating mesa was formed by phosphoric acid-based wet etching down to the InAlAs buffer layer. Source and drain electrodes were defined by electron beam lithography (EBL) with a 2.4-  $\mu m$  distance. Ti/Pt/Au (15 nm/15 nm/50 nm) was evaporated and lifted off to form the source and drain contacts, with contact resistance measured to be 0.023  $\Omega$  •mm and the specific contact resistivity 8.75E-8  $\Omega$  •cm² by TLM method.

Subsequently, the trilayer e-beam resist process was applied to fabricate 50-nm-gate-length T-gates. The gate process was developed by EBL with a PMMA/Al/UVIII (200 nm/10 nm/800 nm) resist stack, which is shown in Fig. 2. The top UVIII resist was exposed by a small dose and wide line. After that, the gate head was determined by TMAH development and rinsed in DI water. Subsequently, the gate foot was defined on a single layer of PMMA resist and was exposed by a big dose and narrow line. This approach allows better focusing at the gate foot exposure step because of the thin PMMA resist. As a result, this process scheme allows a small  $L_{\rm g}$ . After that, the 200 nm gate recess was etched to InP etch-stop layer by  ${\rm H_3PO_4}$ -solution, and a Ti/Pt/Au (25 nm/25 nm/

350 nm) T-gate was evaporated and lifted off. The length of the T-Gate is 54.4 nm, as shown in Fig. 3. Finally, the Ti/Au (15 nm/400 nm) connection pads were evaporated for on-wafer DC and RF characteristics measurements.

### 2 Results and Discussion

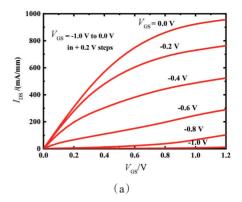

DC properties were characterized by using a HP4142 semiconductor parameter analyzer at room temperature. Figure 4 (a) shows the current-voltage (I-V)characteristics of the HEMT with  $L_{\alpha}$  = 54.4 nm and gate width  $W_{\mu} = 2 \times 50 \, \mu \text{m}$  at room temperature. The gatesource voltage  $(V_{GS})$  is increased from -1.0 V to 0.0 V with step of +0.2 V, and the drain-source voltage  $(V_{DS})$ changes from 0 V to 1.2 V. The  $I_{DS,max}$  @  $V_{GS}$  = 0.0 V is 957 mA/mm. The  $I_{DS, max}$  is enhanced compared to our previously reported InP HEMTs<sup>[14]</sup> and is attributed to the reduction of gate length. The device shows a small value of ON-resistance ( $R_{\rm on} = 0.667 \ \Omega \cdot \text{mm}$ ) due to a relatively narrow gate recess. Because the narrow gate recess leads to reduction of  $R_s$  and  $R_n$  [15]. Moreover, the kink effect of the device is negligible due to the introduction of the InP etching-stopper layer.

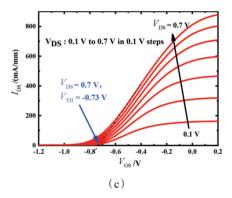

Figure 4 (b) plots the measured transconductance  $(g_{\rm m})$  of the  $L_{\rm g}$  = 54. 4 nm device as a function of  $I_{\rm DS}$ , for various vaules of  $V_{\rm DS}$  from 0. 1 V to 0. 7 V in + 0. 1 V steps. A maximum extrinsic transconductance  $g_{\rm m.max}$  of 1 265 mS/mm is achieved at  $V_{\rm DS}$  = 0. 7 V. The pinch-off voltage is about -0. 73 V at  $V_{\rm DS}$  = 0. 7 V as shown in Fig. 3(c).

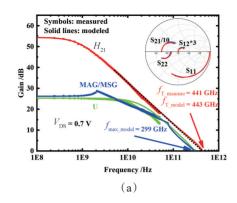

The RF characteristics were measured using an Agilent E8363B PNA vector network analyzer from 0. 1 GHz to 50 GHz. Before the RF test, the equipment was calibrated to eliminate systematic errors due to the environment or test equipment. In order to accurately obtain the S-parameter of the device, we calibrated the test reference surface to the GSG test probe tip. The open and short structures were used to substract pad-related capacitance and inductance components from measured S-parameters. Then, the values of a short-circuit current gain  $(H_{21})$ , a maximum available gain and a maximum stable gain (MAG/MSG), and a Mason's unilateral gain (U) were plotted in Fig. 5 (a). The bias condition was at  $V_{\rm GS}$  = -0. 35 V and  $V_{\rm DS}$  = 0. 7 V.

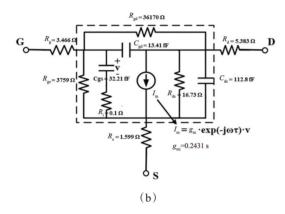

Since the test frequency range was limited from 0. 1 GHz to 50 GHz, we obtained a value of  $f_T$  = 441 GHz by extrapolating the measured  $H_{21}$  with a slope of -20 dB/dec. Regarding  $f_{\rm max}$ , it cannot be directly extracted from the measured U or MAG/MSG. This is because it is difficult to observe a decline in the MAG/MSG frequency curve with a slope of -20 dB/dec in a limited test range. Therefore, if the frequency curve of MAG/MSG is extrapolated with -20 dB/dec at 50 GHz, the  $f_{\rm max}$  obtained is a conservative result. So, we constructed a small-signal model that yielded a well behaved U with a single-pole system, as shown in Fig. 5 (b) [16]. Using the small-signal model, the values of  $f_{\rm max}$  = 299 GHz and  $f_T$  = 443 GHz were estimated accurately. The measured  $f_{\rm T_{measure}}$  and the modeled  $f_{\rm T_{model}}$  are similar, increasing the credibility of

Fig. 4 (a) DC output characteristics, (b)  $g_m$  against  $I_{DS}$ , and (c) transfer characteristics of the HEMT 图 4 HEMT的 (a)直流输出特性,(b)跨导,(c) 传输特性

our model.

The  $f_{\rm T}$  and  $f_{\rm max}$  are expressed as equtions (1) and (2):

$$f_T = \frac{g_{\text{mi}}}{2\pi \{(C_{\text{gs}} + C_{\text{gd}})[1 + g_{\text{ds}}(R_{\text{s}} + R_d)] + C_{\text{gd}}g_{\text{mi}}(R_{\text{s}} + R_d)\}} \quad , (1)$$

$$f_{\text{max}} = \frac{f_{T}}{\sqrt{4g_{\text{ds}}(R_{g} + R_{i} + R_{s}) + \frac{2C_{\text{gd}}}{C_{\text{gs}}}(\frac{C_{\text{gd}}}{C_{\text{gs}}} + g_{\text{mi}}(R_{i} + R_{s}))}}},(2)$$

Where  $C_{\rm gs}$  and  $C_{\rm gd}$  are the capacitances in between gate to source and gate to drain;  $R_{\rm g}$ ,  $R_{\rm S}$ , and  $R_{\rm D}$  are the parasitic resistances of gate, source and drain;  $g_{\rm mi}$  is the intrinsic transconductance;  $g_{\rm ds}$  is the conductance between drain and source.

Fig. 5 (a) The measured and modeled  $H_{21}$ , MAG/MSG and U gains versus frequency for the  $L_{\rm g}=54.4$  nm InGaAs/InAlAs HEMT at  $V_{\rm GS}=-0.35$  V and  $V_{\rm DS}=0.7$  V, and (b) small-signal equivalent circuit model used in pervious work [16] 图 5 (a)在  $V_{\rm GS}=-0.35$  V 和  $V_{\rm DS}=0.7$  V 时,栅长为 54.4 nm 的 InGaAs/InAlAs HEMT 器件,其  $H_{21}$ ,MAG/MSG 和 U 的测试结果

和模型结果与频率的关系,以及(b)小信号等效电路模型[16]

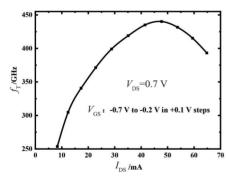

Fig. 6 Measured  $f_{_T}$  against  $I_{_{

m DS}}$  of the  $L_{_g}$  = 54. 4 nm InGaAs/InA-lAs HEMT with  $V_{_{

m DS}}$  = 0. 7 V 图 6 在  $V_{_{

m DS}}$  = 0. 7 V 时,InGaAs/InAlAs HEMT 的 fT 随  $I_{_{

m DS}}$ 的变化

Equations (1) and (2) suggest that  $C_{\rm gs}$ ,  $C_{\rm gd}$ ,  $R_{\rm S}$ ,  $R_{\rm D}$ ,  $g_{\rm mi}$  and  $g_{\rm ds}$  are the key parameters that affect  $f_{\rm T}$  and  $f_{\rm max}$ . Table 1 shows small-signal model parameters. These key parameters are all related to the size of the gate recesse and gate length. In terms of  $f_{\rm T}$ , the small gate length reduces capacitances and increases  $g_{\rm mi}$ . At the same time, the narrow gate recess also reduces the  $R_{\rm S}$  and  $R_{\rm D}$ . So, these affects lead to a higher  $f_{\rm T}=441~{\rm GHz}$ .

However, the narrow gate recesse correspond to larger values of  $C_{\rm gd}/C_{\rm gs}$ , and the shorter gate length leads to larger  $R_{\nu}$  and  $g_{\rm ds}$ , which leads to a smaller  $f_{\rm max} = 299$  GHz.

Figure 6 plots the extracted  $f_T$  as a function of  $I_{\rm DS}$  for the same device at  $V_{\rm DS}$  = 0.7 V, which consists with the  $g_{\rm m}$  against  $I_{\rm DS}$  in Fig. 4. The  $f_T$  of the device exceeds 400 GHz over a wide range of  $I_{\rm DS}$ .

Table 2 shows the reported the performance of In-GaAs/InAlAs HEMTs with  $L_{\rm g}$  from 50 nm to 75 nm. What these devices have in common is that the channel of devices are indium-rich InGaAs. And Pt buried gate technology is used to decrease the gate-to-channel distance, resulting the excellent RF performance. Although the values of  $g_{\rm m. max}$  and  $f_{\rm T}$  are quite different, the larger  $g_{\rm m. max}$  corresponds to higher  $f_{\rm T}$  in this table. Compared with these results, our device achieved the  $f_{\rm T}$  of over 400 GHz with the lowest  $g_{\rm m. max}$ , and we need to improve  $f_{\rm T}$  through further increasing  $g_{\rm m. max}$  in the future.

### 3 Conclusion

In summary, we have successfully designed and fabricated a 54.4 nm T-gate InGaAs/InAlAs InP-based HEMT with  $f_{\scriptscriptstyle T} > 400$  GHz. In order to optimize the parasitic resistances, we adopt a narrow gate recess technology. As a result, the  $f_{\scriptscriptstyle T}$  reaches as high as 441 GHz with a  $g_{\scriptscriptstyle \text{m.max}}$  of 1265 mS/mm. The  $f_{\scriptscriptstyle T}$  is expected to be promoted through further increasing  $g_{\scriptscriptstyle \text{m.max}}$  by adopting an Indiumrich channel and a Pt buried gate technology.

#### References

- [1] Grossman E N, Leong K, Mei X, et al. Low-frequency noise and passive imaging with 670 GHz HEMT low-noise amplifiers [J]. IEEE Transactions on Terahertz Science and Technology, 2014, 4 (6): 749-752.

- [2] Kallfass I, Harati P, Dan I, et al. MMIC chipset for 300 GHz indoor wireless communication [C]. 2015 IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems (COMCAS), 2015; 1-4.

- [3] Schleeh J, Wadefalk N, Nilsson P. -Å., et al. Cryogenic broadband ultra-low-noise MMIC LNAs for radio astronomy applications [J]. *IEEE Transactions on Microwave Theory and Techniques*, 2013, 61 (2): 871-877.

- [4] Zhong Y H, Yang B, Chang MM, et al. Enhancement of radiation hardness of InP-based HEMT with double Si-doped plane [J]. Chinese Physics B, 2020, 29(03): 532-536.

- [5] Mei X, Yoshida W, Lange M, et al. First demonstration of amplification at 1 THz using 25-nm InP high electron mobility transistor process[J]. IEEE Electron Device Letters, 2015, 36(4): 327-329.

- [6] Jo Hyeon–Bhin , Yun Seung–Won , Kim Jun–Gyu , et al.  $L_{\rm g}=19$  nm  ${\rm In_{0.8}Ga_{0.2}As}$  composite–channel HEMTs with  $f_{\rm T}=738$  GHz and  $f_{\rm max}=492$  GHz [C]. 2020 IEEE International Electron Devices Meeting (IEDM) , 2020; 8.4.1–8.4.4.

- [7] Kim D. –H. , Brar B., del Alamo J. A..  $f_{\rm T}=688$  GHz and  $f_{\rm max}=800$  GHz in  $L_{\rm e}=40$  nm  ${\rm In_{0.7}Ga_{0.3}As}$  MHEMTs with  $g_{\rm m_{\rm max}}>2.7$   $m_{\rm s}/\mu{\rm m}$  [C]. 2011 International Electron Devices Meeting, 2011; 13.6.1–13.6.4.

- [8] Yun D Y, Jo H B, Son S W, et al. Impact of the source-to-drain spacing on the DC and RF characteristics of InGaAs/InAlAs highelectron mobility transistors [J]. IEEE Electron Device Letters, 2018, 39(12): 1844-1847.

- [9] Jo H B, Baek J M, Yun D Y, et al.  $L_{\rm g}$ = 87 nm InAlAs/InGaAs highelectron–mobility transistors with a  $g_{\rm m,max}$  of 3 S/mm and  $f_{\rm T}$  of 559 GHz [J]. IEEE Electron Device Letters, 2018, 39(11): 1640–1643.

- [10] Barsky M., Biedenbender M., Mei X., et al. Advanced InP and GaAs HEMT MMIC technologies for MMW commercial products [C]. 2007 65th Annual Device Research Conference, 2007: 147-148.

Table 1 Small-signal model parameters of the  $L_{\rm g}$  = 54.4 nm InGaAs/InAlAs HEMTs at  $V_{\rm DS}$  = 0.7 V, with different structures

表1  $V_{DS} = 0.7$  V时,栅长为54.4 nm的 InGaAs/InAlAs HEMT的小信号模型参数

| $C_{\rm gs}$ [ fF/mm ]                                | $C_{ m gd}$ [fF/mm]                                     | $C_{ m ds}$ [fF/mm]                         | $g_{\mathrm{mi}}$ [mS/mm]                               | $g_{ m ds}$ [ mS/mm ]                   | $R_i \left[ \Omega ullet \mathrm{mm}  ight]$ | $R_{_{\!g}}[\Omega{ullet}\mathrm{mm}]$ |

|-------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|---------------------------------------------------------|-----------------------------------------|----------------------------------------------|----------------------------------------|

| 322. 1                                                | 134. 1                                                  | 1 124                                       | 2 431                                                   | 597. 7                                  | 0.01                                         | 0. 346 6                               |

| $C_{_{\mathrm{D}}}\left[\Omegaullet\mathrm{mm} ight]$ | $R_{_{\mathrm{S}}}\left[\Omega{ullet}\mathrm{mm} ight]$ | $R_{ m gs}  [ \Omega  { m f e}  { m mm}  ]$ | $R_{ m gd} \left[  \Omega  { m ullet}  { m mm}   ight]$ | $f_{\mathrm{T\_measure}}[\mathrm{GHz}]$ | $f_{\mathrm{T\_model}}$ [ GHz ]              | $f_{ m max\_model} [ { m GHz} ]$       |

| 0. 538 3                                              | 0. 159 9                                                | 375. 9                                      | 3 617                                                   | 441                                     | 443                                          | 299                                    |

Table 2 Comparison with published InGaAs(InAs)/InAlAs HEMTs with L<sub>g</sub> from 50 nm to 75 nm 表 2 与已发表的栅长从50 nm到75 nm的InGaAs(InAs)/InAlAs HEMT性能的比较

| Ref.      | $L_{ m g}/{ m nm}$ | Gate metal  | Channel                               | $g_{\rm m}/({\rm mS/mm})$ | $\rm f_T/GHz~(\it V_{\rm DS}/V)$ | $f_{max}/GHz (V_{DS}/V)$ |

|-----------|--------------------|-------------|---------------------------------------|---------------------------|----------------------------------|--------------------------|

| 17        | 50                 | Pt/Ti/Pt/Au | InAs                                  | 2 000                     | 496 (0.6)                        | 400 (0.6)                |

| 18        | 50                 | Pt/Ti/Pt/Au | $In_{0.7}Ga_{0.3}As$                  | 1 750                     | 465 (0.75)                       | 1 060 (0.75)             |

| 19        | 60                 | Pt/Ti/Pt/Au | InAs                                  | 2 100                     | 580 (0.6)                        | 675 (0.6)                |

| 20        | 60                 | Pt/Ti/Pt/Au | InAs                                  | 2 114                     | 710 (0.5)                        | 478 (0.5)                |

| 21        | 70                 | Ti/Pt/Au    | $In_{0.7}Ga_{0.3}As$                  | 1 600                     | 310 (1.2)                        | 540 (1.2)                |

| 22        | 75                 | Ti/Pt/Au    | InAs                                  | 1 331                     | 260 (1.0)                        | 800 (1.0)                |

| This work | 54. 4              | Ti/Pt/Au    | ${ m In}_{0.53}{ m Ga}_{0.47}{ m As}$ | 1 265                     | 441 (0.7)                        | 299 (0.7)                |

- [11] Barsky M, Biedenbender M, Mei X, et al. Advanced InP and GaAs HEMT MMIC technologies for MMW commercial products [C]. 2007 65th Annual Device Research Conference, 2007: 147-148.

- [12] Kim Dae-Hyun, del Alamo J A, Lee Jae-Hak, et al. The impact of side-recess spacing on the logic performance of 50 nm InGaAs HEMTs [C]. 2006 International Conference on Indium Phosphide and Related Materials Conference Proceedings, 2006: 177-180.

- [13] Tong Zhihang, Ding Peng, Su Yongbo, et al. Surface improvement of InAlAs/InGaAs InP-Based HEMT through treatments of UV/ozone and TMAH [J]. IEEE Journal of the Electron Devices Society, 2020, 8: 600-607.

- [14] Tong Zhihang, Ding Peng, Su Yongbo, et al. Influences of increasing gate stem height on DC and RF performances of InAlAs/InGaAs InP-based HEMTs [J]. Chinese Physics B, 2021, 30(1): 018501.

- [15] Feng Ruize, Wang Bo, Cao Shurui, et al. Impact of symmetric gaterecess length on the DC and RF characteristics of InP HEMTs [J]. Chinese Physics B, 2022, 31(01): 788-792.

- [16] Wang Yanfu, Wang Bo, Feng Ruize, et al. Heterogeneous integration of InP HEMTs on quartz wafer using BCB bonding technology [J]. Chinese Physics B, 2022, 31(1): 018502.

- [17] Hideaki Matsuzaki, Takashi Maruyama, Toshihiko Koasugi, et al.

"Lateral scale down of InGaAs/InAs composite-channel HEMTs with

- tungsten-based tiered ohmic structure for 2–S/mm  $g_m$  and 500–GHz  $f_T$  [J]. IEEE Transactions on electron devices, 2007, **54** (3): 378–384

- [18] Kim D H, Alamo J a D, Chen P, et al. 50-nm E-mode In<sub>0</sub>.7Ga0. 3As PHEMTs on 100-mm InP substrate with fmax> 1 THz [C]. 2010 International Electron Devices Meeting, 2010:: 30.6. 1-30.6. 4..

- [19] Kim T. -W., Kim D. -H., del Alamo J. A. 60 nm self-aligned-gate InGaAs HEMTs with record high-frequency characteristics [C]. 2010 International Electron Devices Meeting, 2010; 30.7.1-30.7.4.

- [20] Chang E Y, Kuo C I, Hsu H T, et al. InAs thin-channel high-electron-mobility transistors with very high current-gain cutoff frequency for emerging submillimeter-wave applications [J]. Applied Physics Express, 2013, 6(3): 034001.

- [21] Zhang L, Feng Z, Xing D, et al. 70 nm gate-length THz InP-based In<sub>0.7</sub>Ga<sub>0.3</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As HEMT with fmax of 540 GHz [C]. 2014 XXXIth URSI General Assembly and Scientific Symposium (URSI GASS), 2014: 1-4.

- [22] Samnouni M., Wichmann N., Wallart X., et al. 75 nm Gate length PHEMT with f<sub>max</sub>=800 GHz using asymmetric gate recess: RF and noise investigation [J]. IEEE Transactions on Electron Devices, 2021, 68(9): 4289-4295.