文章编号: 1001-9014(2021)02-0184-05

# Three-dimensional structure analysis of Schottky barrier diode in CMOS technology for terahertz imaging

$\label{eq:cuide} {\rm CUI} \ {\rm Da-Sheng}^*, \quad {\rm YANG} \ {\rm Jia-Ming}, \quad {\rm YAO} \ {\rm Hong-Xuan}\,, \quad {\rm LYU} \ {\rm Xin}$

(Beijing Key Laboratory of Millimeter Wave and Terahertz Technology, School of Information and Electrics, Beijing Institute of Technology, Beijing 100081, China)

**Abstract:** A simple and effective design method for high cut-off frequency Schottky barrier diode is proposed and implemented. The cut-off frequency of the processed Schottky barrier diode is about 800 GHz, which can reach about 1 THz with the optimized parameters through the test results and simulation data in SMIC 180 nm process. The integrated detector including antennas, matching circuit and Schottky barrier diode is completed, whose test-ed responsivity could achieve 130 V/W and noise equivalent power is estimated to be 400 pW/ $\sqrt{\text{Hz}}$  at 220 GHz. The imaging experiment of invisible liquid surface in ceramic bottles has been completed and good results have been achieved.

Key words: complementary metal oxide semiconductor (CMOS), detector, imaging, Schottky barrier diode, terahertz

PACS: 07. 57. Kp

## 用于太赫兹成像的 CMOS 肖特基二极管三维结构研究

## 崔大圣\*,杨佳铭,姚宏璇,吕 昕

(北京理工大学信息与电子学院毫米波与太赫兹技术北京市重点实验室,北京100081)

摘要:提出了一种简单、科学、有效的高截止频率肖特基势垒二极管设计方法。通过SMIC 180 nm 工艺制备的肖特基二极管的截止频率为800 GHz,分析测试结果和仿真数据优化后的肖特基势垒二极管截止频率可以达到1 THz 左右。完成了包括天线、匹配电路和肖特基势垒二极管的集成探测器,在220 GHz 下其测试响应率可达 130 V/W,等效噪声功率估计为400 pW/VHz。完成了陶瓷瓶内不可见液面的成像实验并取得了良好的效果。 关键 词:互补金属氧化物半导体;检波器;成像;肖特基二极管;太赫兹(THz)

中图分类号:TN454

#### 文献标识码:A

收稿日期:2020-06-29,修回日期:2020-12-25

## Introduction

Lately, focus on terahertz (THz) technology has been growing rapidly owing to its great potential in the fields of imaging, medical, communication, astronomy, etc. <sup>[1-2]</sup>. A number of studies have been reported on THz imaging system, which is closer than spectroscopy to being commercialized in the near future<sup>[3]</sup>. complementary metal oxide semiconductor (CMOS) technology attracts high attention in THz imaging filed with its low cost and high integration, which meets the needs of THz largescale imaging array<sup>[4]</sup>.

Two major THz detectors in the CMOS field have been extensively studied, filed-effect transistor (FET) detectors based on plasma-wave detection theory and Schottky barrier diode (SBD) detector based on square law detector theory<sup>[5-6]</sup>. Compared with FET detectors, SBD detectors have obvious advantages in responsivity, which is extremely important for THz imaging owing to the inherent high spatial loss of THz wave<sup>[7-8]</sup>. Since V. Milanovic and Sankraran successively realize Schottky contact in CMOS process by metallizing the contact on the n-well and contacting the metal silicide with the substrate, many related studies have been done on CMOS SBD<sup>[9]</sup>. Nevertheless, there is no SBD applicable to THz band in the existing standard CMOS library, which is a hot point and difficulty in the THz study field.

The CMOS technology-based THz detectors with dif-

**Received date:** 2020-06-29, revised date: 2020-12-25

Foundation items: Supported by National Natural Science Foundation of China (61527805)

Biography: CUI Da-Sheng (1992-), male, Binzhou, China. Ph. D. student. Research area involves terahertz device and quasi-optical component E-mail:dscui@bit.edu.cn

<sup>\*</sup> Corresponding author: E-mail: dscui@bit. edu. cn

ferent detection mechanisms including plasma modes and Schottky barrier diodes have very high requirements for cut-off frequency. The cut-off frequency of SBD is closely related to the minimum size that CMOS technology can achieve. Many high cut-off frequency detectors come to the fore with the progress of technology. For example, a 0. 86-THz 4 × 4 array CMOS technology-based SBD imager is reported with raster scan measurement<sup>[10-11]</sup>, and a 1 × 240 array compound InGaAs SBD imager is demonstrated as a real-time 1-D line scanner<sup>[12]</sup>.

2期

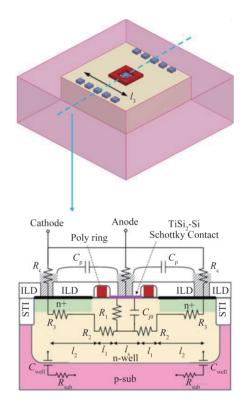

The progress of technology has brought a great leap forward to the overall index of SBD detectors, but the influence of design factors on the index of detectors under the same technology can not be underestimated. There are two main ways to realize Schottky barrier diode in CMOS standard process: shallow trench isolation technology and Polysilicon gate separation technology, shown in Fig. 1. Polysilicon gate separation SBD has less interference to current path, less channel impedance and higher cut-off frequency, which means that it has greater potential in THz imaging field<sup>[13]</sup>.

Fig. 1 Structure of two kinds of SBDs (a) shallow trench isolation SBD, (b) polysilicon gate separation SBD

图 1 两种肖特基二极管结构 (a) 浅沟道隔离肖特基二极管, (b) 多晶硅栅隔离肖特基二极管

In this paper, we design a high-performance terahertz detector based on self-designed SBD in 180-nm CMOS foundry technology. In Sect. I, the three-dimensional structure of the polysilicon gate separation SBD is built, and the main factors affecting the cut-off frequency of Schottky barrier diode is analyzed and simulated. In Sect. II, we verify and optimize the data according to the results of the tape-out, and find out the technical points of designing a high cut-off frequency diode under the standard CMOS process. In Sect. III, we design a detector with a high-gain on-chip antenna and the key circuit architecture. Then, the terahertz imaging platform is built and the imaging experiment of liquid level detection in wine bottle is completed.

# 1 Structure analysis of Schottky barrier diodes

The three-dimensional structure of the diode is analyzed in detail to find the design method of high cut-off frequency diodes under the technological limitation, that is particularly important to terahertz detectors. The performance of polysilicon gate separation SBD is better than that of shallow trench isolation SBD in cut-off frequency, which determines our next major analysis of polysilicon gate separation SBD.

Fig. 2The three-dimensional structure and two-dimensionalprofile of polysilicon gate separation SBD图 2多晶硅栅隔离肖特基二极管的三维和二维结构示意图

As shown in Fig. 2, the polysilicon gate separation SBD separates Schottky contact between metal and lightly doped N-well and Ohmic contact between metal and heavily doped N-well by polysilicon ring.

Zero-bias cut-off frequency of SBD:

$$f_{co} = \frac{1}{2\pi R_{s} C_{0}} \qquad , \quad (1)$$

$R_{\rm s}$  is series resistance and  $C_0$  is diode capacitance at zero bias. The expressions of  $R_{\rm s}$  and  $C_0$  are derived as below. Individual components contributing to  $R_{\rm s}$  and  $C_0$  are shown in Fig. 2.

$$R_{\rm s} \approx R_1 + R_2 + R_3 + R_{\rm c}$$

, (2)

$$R_{s} \approx R_{v} + \frac{R_{\text{nwell}}}{28.6} + R_{\text{poly}} \left(\frac{l_{1}}{4l_{s}}\right) + R_{n^{*}} \left(\frac{l_{2}}{4(l_{s}+2l_{1})}\right) + R_{c}, (3)$$

$$C_{0} = l_{s}^{2} \sqrt{\frac{qN_{\text{D}}\varepsilon_{\text{Si}}}{2\phi_{n}}} + C_{p} , \quad (4)$$

where,  $R_v$  is the vertical component of  $R_1$ ,  $R_{nwell}$  is n-well sheet resistance,  $R_{poly}$  is the n-well sheet resistance under the poly separation ring,  $R_{n+}$  is salicide n+ sheet resistance,  $R_e$  is the overall of resistance of vias and contacts,  $N_{\rm D}$  is n-well doping density,  $\varepsilon_{\rm Si}$  is the permittivity of silicon,  $\Phi_{\rm B}$  is the built-in potential, and  $C_{\rm p}$  is the parasitic capacitance of metal terminals. The factor of 1/28. 6 is derived from the base-spreading resistance model in Ref. [14]. In addition,  $l_s$  is the side length of square Schottky contact,  $l_1$  is the width of polysilicon ring,  $l_2$  is the length of polysilicon to cathode metal contact. The coefficients 1/4 and 1/2 in Eq. 3 correspond to the parallel calculation of 4 polysilicon ring and 2 cathode metal in the diode structure diagram, respectively.

From the above analysis, we can get that  $l_s$  is approximately inversely proportional to the cut-off frequency, that is, smaller anode contact area can get higher cutoff frequency, which is described in many articles. Owing to the obvious limitation of technology on  $l_s$  and  $l_1$ , our main research objectives are  $l_2$  and  $l_3$ , which only affects a part of the total resistance and capacitance. And their changes have the opposite effect on the resistance and capacitance values, that requires us to reverse design according to the actual results.

Fig. 3 Simulation result of the effect of  $l_2$  and  $l_3$  on resistance and capacitance (a) capacitance curve, (b) resistance curve 图 3  $l_2$ 和 $l_3$ 对电阻电容的影响分析 (a) 电容曲线,(b) 电阻曲 线

The simulation results of  $l_2$  and  $l_3$  using Sentaurus and HFSS software with fixed N-well size are shown as Fig. 3.  $R_x$  and  $C_x$  respectively represent the total resis-

tance and the parasitic capacitance  $C_{p}$  between the positive electrodes and negative electrodes. The length of  $l_3$ determined by the number of vias in the negative electrode cannot be continuously changing due to process limitation. In Fig. 3, via X indicates that the negative electrode consists of X vias. As we can see from Fig. 3, with the increase of  $l_2$ , the resistance will increase and the capacitance will decrease, while  $l_3$  has the opposite effect. It is important to observe that this change is not linear, which shows that the effect of  $l_2$  on parasitic capacitance decreases when  $l_2$  increases to 1.4  $\mu$ m, and the effect of  $l_3$  on resistance can be neglected when the number of vias reaches 7. So far, we cannot determine the optimal size of the SBD, because the simulation results are only a part of the total resistance and capacitance of the SBD. Next, we need to take the changed part into the total impedance and capacitance, and then substitute it into Eq. 1 to get the most suitable size of the SBD.

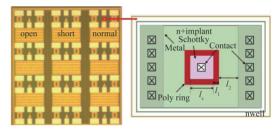

### 2 Chip testing and result analysis

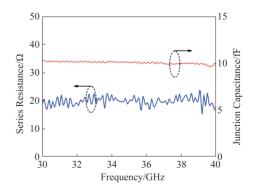

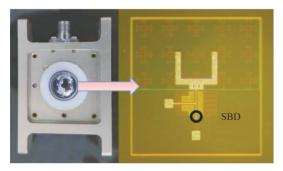

The designed SBDs are fabricated in SMIC 180 nm process, shown in Fig. 4. The DC characteristics are measured by using Agilent B1500A semiconductor parameter analyzer, and the S-parameters are measured by using Agilent E8363B vector network analyzer. When  $l_s$  and  $l_1$  take the minimum value of process,  $l_2=1.4 \,\mu\text{m}$  and  $l_3=\text{via5}$ , the series resistance  $(R_s)$  and diode capacitance  $(C_0)$  of 8 SBD are 20  $\Omega$  and 10 fF respectively measured by open-short method<sup>[15]</sup>. The test results of eight parallel SBD are shown in Fig. 5.

Fig. 4 Chip physical photo and the SBD plane diagram 图4 芯片照片和二极管平面示意图

Fig. 5 Measured  $R_s$  and  $C_0$  for the 8 cells Schottky barrier diode 图 5 8个并联肖特基二极管的 $R_s$ 和 $C_0$ 测试结果

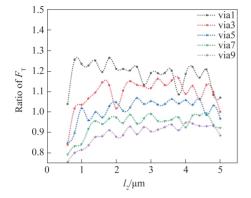

Based on the measured results, the simulation results are brought into the above results and normalized to calculate the cut-off frequency  $F_{\rm T}$ , which represents the ratio of the cut-off frequency to the cut-off frequency at  $l_2$ = 1.4 µm and  $l_3$ =via5, shown in Fig. 6.

Fig. 6 Changes in ratio of  $F_{\rm T}$  with  $l_2$  and  $l_3$  图 6 不同  $l_2$ 和  $l_3$ 下的归一化截止频率  $F_{\rm T}$

As we can see from Fig. 6, the diode has the highest cut-off frequency in the current process when  $l_3$  is vial and  $l_2$  is between 1 µm to 2 µm. According to Eq. 1, the cut-off frequency is about 800 GHz when  $l_2=1.4$  µm and  $l_3=via5$ , and the optimal design scheme can reach about 1 THz when  $l_3=via1$  and  $l_2=1\sim2$  µm.

The comparison of previous work is shown in Table. 1. It can be seen that the work of this paper is on the leading level in same technology. But the cut-off frequency of diode will be greatly improved with the improvement of technology, which also indicates that CMOS technology has great potential in terahertz field.

Table 1 Comparison of previous works 表1 与以往工作对比

| Cut-off frequency | Article                             |

|-------------------|-------------------------------------|

| 700 GHz           | [13]                                |

| 1.2~1.5 THz       | [16]                                |

| 400 GHz           | [17]                                |

| 800 GHz~1 THz     | This                                |

|                   | 700 GHz<br>1. 2~1. 5 THz<br>400 GHz |

## 3 The detector and imaging test

The detector consists of on-chip antenna, matching circuit and SBD, shown in Fig. 7. The silicon lens used

Fig. 7 Photographs of the detector package box and the Chip 图 7 检波器盒体照片和芯片照片

to further increase gain is packaged with the chip forming the final imaging unit. It is calculated through testing that the antenna gain at 220 GHz is 32 dB, in which the contribution of lens is about 22 dB. The tested responsivity of the detector could achieve 130 V/W and the noise equivalent power is estimated to be 400 pW/ $\sqrt{\text{Hz}}$ .

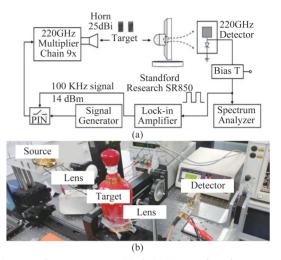

Fig. 8 Imaging test system (a) the 220 GHz imaging test setup, (b) the photo of 220 GHz imaging platform 图 8 成像测试系统 (a) 220 GHz 成像系统框图,(b) 220 GHz 成 像平台照片

Figure 8 shows the imaging test setup and the photo of imaging platform using the designed detector. A multiplier chain driven by signal source (Agilent E8257D) forms terahertz transmitter. When the output power of the signal source is 14 dBm, the maximum output power of the multiplier chain is 12 dBm. A detector is used to receive THz waves passing through the target. And a lock-in amplifier measures the rms value of output voltage for the detector and generates 100 KHz signals for amplitude-modulation (AM) at 220 GHz. The DC drifts and low frequency noise 1/f are eliminated.

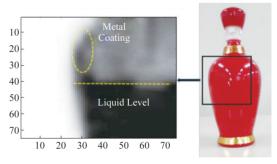

Fig. 9 Imaging results of liquid level in a ceramic bottles 图 9 陶瓷瓶内液面成像结果

### 4 Conclusion

In the same process, polysilicon gate separation SBD has higher cut-off frequency than shallow trench isolation SBD. When designing polysilicon gate separation SBD in SMIC 180 nm process, the number of vias in cathode should be as few as possible to increase cut-off frequency. For polysilicon gate separation SBD, when the number of vias constituting the cathode is 1 and the distance between the cathode and the polysilicon is  $1\sim2$  µm, the cut-off frequency is the highest, which is about 1 THz. The liquid level imaging experiment in ceramic bottle proves that THz wave has great potential in invisible object detection for its good penetration.

### References

- [1] Peter H, Siegel. Terahertz technology [J]. IEEE Transactions on Microwave Theory and Techniques, 2002, 50(3):910–928.

- [2] Zhu M, Li X, Chung S, et al. Photo-induced selective gas detection based on reduced graphene oxide/Si Schottky diode [J]. Carbon, 2015, 84:138-145.

- [3] Dyakonov M, Shur M. Detection, mixing, and frequency multiplication of terahertz radiation by two-dimensional electronic fluid [J]. *IEEE Transactions on Electron Devices*, 1996, 43(3):380-387.

- [4] Han S P, Park J W, Ko H, et al. Terahertz imaging using InGaAs Schottky barrier diode array detectors [C]. International Conference on Infrared. 2013.

- [5] Ryu M W, Lee J S, Kim K S, et al. High-performance plasmonic THz detector based on asymmetric FET with vertically integrated antenna in CMOS technology [J]. *IEEE Transactions on Electron Devic*es, 2016, 63(4):1742-1748.

- [6] Knap W, Teppe F, Meziani Y, et al. Plasma wave detection of subterahertz and terahertz radiation by silicon field-effect transistors [J]. Applied Physics Letters, 2004, 85(4): 675-677.

- [7] Zhu M, Song B, Qi M, et al. 1.9-kV AlGaN/GaN lateral Schottky

barrier diodes on silicon [J]. *IEEE Electron Device Letters*, 2015, **36** (4):375–377.

- [8] Shim D, Sankaran S, K. K O. Complementary antiparallel Schottky barrier diode pair in a 0.13- Logic CMOS technology [J]. *IEEE Electron Device Letters*, 2008, 29(6):606-608.

- [9] Seok E, Cao C, Sankaran S, et al. A millimeter-wave Schottky Diode detector in 130-nm CMOS technology [C]. VLSI Circuits, 2006. Digest of Technical Papers. 2006 Symposium on. IEEE, 2006.

- [10] Han R, Zhang Y, Coquillat D, et al. A 280–GHz Schottky diode detector in 130–nm digital CMOS [C]. IEEE, 2011: 2602–2612.

- [11] Han R, Zhang Y, Kim Y, et al. Active terahertz imaging using Schottky diodes in CMOS: array and 860-GHz pixel [J]. IEEE Journal of Solid-State Circuits, 2013, 48(10):2296-2308.

- [12] Han S P, Ko H, Kim N, et al. Real-time continuous-wave terahertz line scanner based on a compact 1 × 240 InGaAs Schottky barrier diode array detector [J]. Optics Express, 2014, 22(23):28977-83.

- [13] Chang W L, Meng C, Huang G W. SBD layout optimization with effect of N-well to p-substrate pn junctions in 0.18 μm CMOS process [C]. 2016 Asia–Pacific Microwave Conference, 2016.

- [14] Rein H, Schroter M. Base spreading resistance of square-emitter transistors and its dependence on current crowding [J]. *IEEE Trans*actions on Electron Devices, 1989, 36(4):770-773.

- [15] Nan L, Mouthaan K, Xiong Y Z, et al. Experimental characterization of the effect of metal dummy fills on spiral inductors [C]. 2007 IEEE Radio Frequency Integrated Circuits Symposium. IEEE, 2007.

- [16] Sankaran S, Kenneth K O. Schottky barrier diodes for millimeter wave detection in a foundry CMOS process [J]. *IEEE Electron Device Letters*, 2005, 26(7):492-494.

- [17] Sankaran S, K. K O. Schottky diode with cutoff frequency of 400 GHz fabricated in 0.18 μm CMOS [J]. *Electronics Letters*, 2005, 41 (8):506-508.