文章编号: 1001 - 9014(2017)05 - 0543 - 07

DOI:10.11972/j.issn.1001 - 9014.2017.05.006

# 86 mV/dec subthreshold swing of back-gated MoS<sub>2</sub> FET on SiO<sub>2</sub>

- (1. Department of Physics, International Center for Quantum and Molecular Structures, and Material Genome Institute, Shanghai University, Shanghai 200444, China;

- State Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Microsystem and Information Technology, CAS, Shanghai 200050, China;

- 3. College of Materials Science and Engineering, Shenzhen Key Laboratory of Special Functional Materials, Shenzhen University, Shenzhen 518060, China;

- 4. Peter Grünberg Institute 9, JARA-FIT, Forschungszentrum Jülich, Jülich 52425, Germany)

**Abstract**: Back-gated (BG) Multi-layer  $MoS_2$  field effect transistors (FETs) have been fabricated on  $SiO_2/Si$  (P<sup>++</sup>) substrate and electrically characterized. By optimizing the fabrication process and scaling down the  $SiO_2$  thickness to 10 nm, the device exhibit excellent switching performance with a subthreshold swing of 86 mV/dec and an  $I_{on}/I_{off}$  ratio ~10<sup>7</sup>. The little hysteresis and small SS jointly suggest tiny magnitude of interface traps or attached oxidants. The noise current induced by gate leakage can affect the measured switch ratio by overwhelming the effective  $I_{off}$  current defined by  $V_{DS}$ . According to the behaviors of  $MoS_2$  FETs expressed by this work and others', BG devices with  $SiO_2$  insulator present good performance and valuable potentials underutilized for rich applications.

**Key words:** MoS<sub>2</sub> FETs, excellent subthreshold swing, SiO<sub>2</sub> dielectric, interface state density **PACS:** 73.21. AC, 73.40. QV

# 具有 86 mV/dec 亚阈值摆幅的 $MoS_2/SiO_2$ 场效应晶体管

刘 强<sup>1,2</sup>, 蔡剑辉<sup>1,2</sup>, 何佳铸<sup>3</sup>, 王翼泽<sup>2</sup>, 张栋梁<sup>2</sup>, 刘 畅<sup>2</sup>, 任 伟<sup>1</sup>, 俞文杰<sup>2</sup>\*, 刘新科<sup>3</sup>\*, 赵清太<sup>4</sup>

(1. 上海大学物理系 量子与分子结构国际中心,材料基因研究院,上海 200444;

- 2. 中科院上海微系统与信息技术研究所,信息功能材料国家重点实验室,上海 200050;

- 3. 深圳大学材料学院,深圳市特种功能材料重点实验室,深圳 518060;

- 4. 德国于利希研究中心,于利希 52425,德国)

摘要:在 $SiO_2/Si(P^{**})$ 衬底上制备了多层 MoS2 背栅器件并进行了测试. 通过合理优化和采用 10 nm  $SiO_2$ 栅氧,得到了良好的亚阈值摆幅 86 mV/dec 和约  $10^7$  倍的电流开关比. 该器件具有较小的亚阈值摆幅和较小的回滞幅度,表明该器件具有较少的界面态/氧化物基团吸附物. 由栅极漏电造成的漏极电流噪声淹没了该器件在小电流( $\sim 10^{-13}$  A)处的信号,限制了其开关比测量范围. 基于本文以及前人工作中 MoS<sub>2</sub> 器件的表现,基于薄层  $SiO_2$  栅氧的 MoS<sub>2</sub> 器件表现出了良好的性能和潜力,显示出丰富的应用前景.

关 键 词: MoS<sub>2</sub> 场效应晶体管;良好的亚阈值斜率; SiO<sub>2</sub> 栅介质; 界面态密度

中图分类号:TN386.2 文献标识码:A

Received date: 2017-05-22, revised date: 2017-06-27

收稿日期:2017-05-22, 修回日期:2017-06-27

Foundation items; Supported by the National Natural Science Foundation of China (61674161, 61504083), Open Project of State Key Laboratory of Functional Materials for Informatics, Public welfare capacity building in Guangdong Province (2015A010103016), and the Science and Technology Foundation of Shenzhen (JCYJ20160226192033020)

Biography: Liu Qiang (1991-), male, Anyang, Master, Research area involves 2D Semiconductor materials and devices. E-mail: qiangliu@ mail. sim. ac. cn \* Corresponding author: E-mail: casan@ mail. sim. ac. cn, xkliu@ szu. edu. cn

# Introduction

Molybdenum disulfide (MoS<sub>2</sub>), as a layered material with atomic thickness and proper bandgap (1.2 eV for multilayers and 1.8 eV for monolayer) [1], has attracted considerable attention for the possibility to extend Moore's law in coming decades  $^{[2\cdot3]}$ . MoS $_2$  is also a potential 2D semiconductor for bio-sensor [4], optical devices<sup>[5]</sup> and flexible circuits<sup>[6-7]</sup>. While monolayer MoS<sub>2</sub> with a thickness of 0.65 nm<sup>[8]</sup> shows good availability in nanoscale devices and optical applications, multi-layer MoS<sub>2</sub> with a certain thickness exhibits higher mobility and better immunity to circumstance-induced scatterings<sup>[9-10]</sup>. In early studies, thermally grown SiO<sub>2</sub> with a thickness of 300 nm, which is in purple color, was proved a good substrate for spotting the layer number of a MoS<sub>2</sub> membrane exfoliated on it<sup>[11]</sup>. Thus the following researchers usually choose 300-nm SiO<sub>2</sub> as the dielectric in fabricating BG mono/multi-layer  $MoS_2$   $FETs^{[12-14]}$  to study the electrical characteristics of MoS2 in different applications. Nevertheless, SiO2 has not been chosen as the top gate oxide when preparing top-gated (TG) FETs with sandwiched MoS<sub>2</sub> membranes, but high-κ dielectric instead. Such device with single-layer MoS<sub>2</sub> surrounded by  $SiO_2$  and  $HfO_2$  has exhibited a high  $I_{on}/I_{off}$  ratio ~  $10^8$ and a very low SS at 74 mV/decade [15], which agrees with the theoretical prediction that high-κ surroundings could effectively screen the coulomb scattering from traps near the conducting channel [10]. As contrast, SiO<sub>2</sub>-based MoS2 devices are seemingly overmatched by a landslide when referring to subthreshold swing  $(SS)^{[14, 16-17]}$ , carrier mobility [18] and on-state current [19]. However, most comparisons above took place between TG/BG devices with thin high-κ insulators and BG devices with thick SiO<sub>2</sub> insulator, and the latter ones' MoS<sub>2</sub> channels are usually exposed to ambient environment. It's not fair to ideologically assume a poor outlook of SiO2-based devices if the following points are noticed: i) SS closely relate with the equivalent oxide thickness (EOT), ii) coulomb scattering in SiO2 circumstance will be decreased when increasing the MoS<sub>2</sub> layer number, iii) foreign impurities from the ambient will severely suppress the device's performance. Actually, a recent research predicted that high-κ dielectrics can increase the electron mobility of a 2D semiconductor only when the impurity density is very high, while clean samples surrounded by low-κ materials such as SiO<sub>2</sub> show a much higher electron mobility than in high- $\kappa$  conditions<sup>[20]</sup>. Thus, comprehensive consideration should be made for MoS2 devices in specific cir-

Compared with preparing high- $\kappa$  dielectric by ALD (atomic layer deposition) or sol-gel method, it is easier to get a high-quality  $\mathrm{SiO}_2$  layer with a uniform thickness by thermal growth.  $\mathrm{SiO}_2$  with a stronger breakdown electric field than that of high- $\kappa$  materials is suitable for high performance BG devices that widely used in bio-chemical sensors, optical detectors and other related researches,

especially when the electrode pads are overlapped by the back gate, which increases the risk of dielectric breakdown and induces a non-negligible gate leakage.

In this work, BG  $\mathrm{MoS_2}$  FETs with  $\mathrm{SiO_2}$  dielectric of different thicknesses were fabricated. The device with a thin  $\mathrm{SiO_2}$  layer (10 nm) performs as well as some reported devices with high- $\kappa$  oxide. An  $I_{\mathrm{on}}/I_{\mathrm{off}}$  ratio ~  $10^7$  and a minimum SS at 86 mV/dec were achieved. It is the best SS value to our knowledge among those  $\mathrm{SiO_2}$ -based BG  $\mathrm{MoS_2}$  FETs.

#### 1 Device fabrication

SiO<sub>2</sub> layers of different thicknesses (10, 20, 30, 50, 100, 200 and 300 nm) were thermally grown on p + + doped silicon wafers ( $\rho$  < 0.001  $\Omega \cdot$  cm), and further confirmed by a SC620 ellipsometer. All the SiO<sub>2</sub> surfaces were treated by O<sub>2</sub> plasma for 5 mins to improve the surface adhesive force, and followed by mechanical exfoliation of MoS<sub>2</sub> films with a scotch tape. To get rid of the residual organic pollutant from the tape, we dipped the wafer in Acetone for 10 mins and in alcohol for 5mins. Considering that the source/drain metal with a low work function (WF) promotes small schottky barriers  $^{\lfloor 19 \rfloor}$ , we chose a 200 nm aluminum (WF ~ 4.2 eV) layer deposited by EBE (electron-beam evaporation) as the contact metal to the MoS₂ membrane. Next, 200°C annealing in a forming gas for 2 hours was carried to further lower the contact barrier<sup>[21]</sup>.

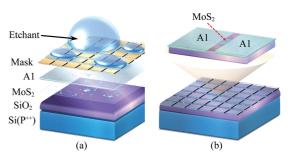

Fig. 1 (a) Fabrication processes of the BG multi-layer  $MoS_2$  FETs. (b) Schematic of the finished chip 图 1 (a) 背栅多层  $MoS_2$  场效应晶体管制备流程,(b) 制备完成的器件芯片

As shown in Fig. 1 (a),  $MoS_2$  sheets of different shapes and thicknesses are randomly distributed on the  $SiO_2$  surface. To expediently fabricate as many devices as possible, we designed a mask with thousands densely arranged square pads. According to the Buffon's needle experiment, a  $MoS_2$  "needle" with several-microns scale will have a good possibility to be contacted by two Al pads. All the pads with 70- $\mu$ m side lengths are separated by 3- $\mu$ m-long channels. And all the pads were defined by ultra-violet lithography technology. Considering the  $MoS_2$  films attached to the  $SiO_2$  surface by Van der Waals force are easily to be washed away in a lift-off process, a mixed solution (10% DI water +5% nitric acid +5% acetic acid +80% phosphoric acid) was chosen to uniformly etch the Al metal that coated on the channel area.

As displayed in Fig. 1 (b), devices with properly positioned  $MoS_2$  sheets were selected with a Leica microscope. The thicknesses of these membranes were measured by a BRUKER AFM. In order to decrease the attached impurities [22-23], all the devices were placed in a vacuum chamber ( $10^{-4}$  mbar) for more than 24 hours before electrical characterization. The electrical tests with Agilent B1505 were finished in one hour after the chips' exposure to the ambient environment.

### 2 Results and discussion

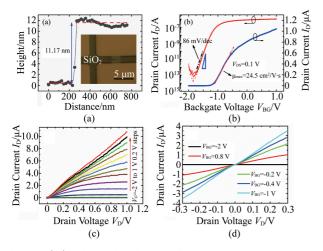

Device with 11. 17 nm (  $\sim 17~{\rm layer})~{\rm MoS_2}$  shown in Fig. 1 (a) was fabricated with a 10 nm SiO<sub>2</sub> layer. Figure 2 (b) displays the device's transfer characteristics with an  $I_{\rm o}$ n/ $I_{\rm off}$  ratio  $\sim 10^7$ , a carrier mobility at 24. 5 cm²/V · s and a SS at 86 mV/dec. It is the best SS value to our knowledge among the reported SiO<sub>2</sub>-based BG devices [12, 16, 24-29]. The testing process in Fig. 2 (b) was carried in a dark chamber at  $T=300~{\rm K}$ , in a step of 0.05 V. The blue triangle shows the ideal SS slope. The interface state density ( $D_{\rm it}$ ) can be estimated by the following equation  $^{[30]}$ :

$$SS = \frac{kT}{q} \ln(10) \times \left(1 + \frac{(C_{\rm s} + C_{\rm it})}{C_{\rm ox}}\right) , \quad (1)$$

where k is the Boltzmann constant, T is the characterization temperature in Kelvin,  $C_{\rm S}$  is the depletion capacitance of  ${\rm MoS_2}$ ,  $C_{\rm it}$  is the  ${\rm MoS_2/SiO_2}$  interface state capacitance, and  $C_{\rm OX}$  is the gate capacitance at  $3.45\times 10^{-7}$  F/cm² (10 nm SiO<sub>2</sub>). When  $V_{\rm G}$  is near to the threshold voltage,  $C_{\rm s}$  can be neglected compared with  $C_{\rm it}$ . Thus, we can further get the effective interface state density by [31]

$$D_{it} = \frac{C_{it}}{q^2} \approx \left(\frac{qSS}{kT \ln(10)} - 1\right) \times \frac{C_{OX}}{q^2} \quad . \quad (2)$$

Fig. 2 (a)The optical image of the BG  $MoS_2$  FET and a thickness scan along the dash line across the  $MoS_2$  sheet. (b) Transfer characteristics,(c) Output characteristics,(d) The details of  $I_{DS}$ - $V_D$  curves across the point of  $V_D$  = 0 V 图 2 (a)背栅  $MoS_2$  场效应晶体管的光学图像,以及  $MoS_2$  薄膜的厚度扫描结果,(b)转移特性曲线,(c)输出特性曲线,(d)  $V_D$  = 0 V 附近的  $I_DS$ - $V_D$  曲线

The interface state density  $D_{\rm it}$  is calculated to be 9.55 ×  $10^{11}/{\rm cm}^2 \cdot {\rm eV}$ , which is a relatively low value among the previous works<sup>[1, 16, 18, 32]</sup>, as indicating less coulomb scattering. A field effect mobility of 24.5 cm<sup>2</sup>/V · s is extracted using<sup>[1]</sup>:

$$\mu = \left[\frac{\mathrm{d}I_{\mathrm{D}}}{\mathrm{d}V_{\mathrm{G}}}\right]_{\mathrm{max}} \times \frac{L}{WC_{\mathrm{OX}}V_{\mathrm{D}}} \qquad , \quad (3)$$

where L/W=0.66,  $V_{\rm D}=0.1$  V. It is a conventional mobility among  ${\rm SiO_2}$ -based BG  ${\rm MoS_2}$  devices [16, 24, 33]. However, the mobility is yet underestimated due to neglecting the contact resistance, which will be discussed subsequently.

The output characteristics with fixed back gate voltages were presented in Fig. 2 (c), the current bending with an increasing  $V_{\rm D}$  is induced by the pinch-off in  ${

m MoS}_2$ channel. Before  $V_{\rm D}$  reaches the pinch-off points, all the output curves arranged in Fig. 2 (d) are almost linear, which suggests a good Al/MoS2 contact. Nevertheless, a recent research indicates that the seemingly Ohmic contact could be a false appearance of a thermally assisted tunneling Schottky barrier<sup>[19]</sup>. According to the Fowler-Nordheim (FN) tunneling current function as described in Ref. [31], both the tunneling intensity and the resistance of Schottky barrier are  $V_{BG}$  dependent. We can briefly express the contact resistance as  $R_c = R_m + R_s$ , where  $R_c$  is the total resistance of the Metal/MoS<sub>2</sub> contacts,  $R_{\scriptscriptstyle m}$  is the voltage independent Ohmic resistance,  $R_{\rm s}$  is the temperature/voltage dependent Schottky barrier resistance.

In a typical two-probe mobility measurement, the voltage dropping across the channel region will be overrated at the presence of  $R_c$ . By assuming that  $R_s$  varies little when the device is overdriven<sup>[35]</sup>, the Y-function method developed by Ref. [34] and verified by Ref. [35] was applied to obtain the  $R_c$ . The resistance induced by source/drain contacts is extracted as 41.5 k $\Omega$ , or 221.2  $\Omega$  · mm. It is a relatively smaller value when compared with that of Refs. [36-38], but obviously higher than that of Refs. [19, 39], which suggest that the device's performance could be further improved by a forward decrease of  $R_c$ . Relevant researches have been developed by Refs. [19, 21, 40-42]. Finally, a modified mobility of 42.3 cm²/V · s is deduced, 72.7% higher than the primary value calculated through the typical method.

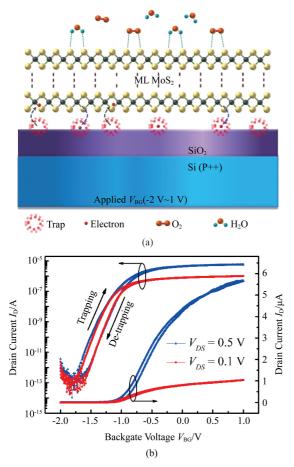

For most BG  $\mathrm{MoS}_2$  FETS with their channel exposed to the ambient environment, hysteresis is commonly exist when taking two-direction gate sweeps. The hysteresis is mainly induced by the trapping and de-trapping processes dominated by the channel potential [43]. As exhibited in Fig. 3 (a), traps not only exist at the  $\mathrm{MoS}_2/\mathrm{SiO}_2$  interface [29], but also forms at the upper face of the  $\mathrm{MoS}_2$  membrane with attached  $\mathrm{H}_2\mathrm{O}$ ,  $\mathrm{O}_2$  and other impurity molecules by Van der Waals force or electrostatic force [44]. For devices fabricated in a rather clean environment, the hysteresis during tests is mainly induced by the foreign impurities from the ambient [16]. Interestingly, the dynamic balance of the absorption magnitude can be changed by the applied gate voltage [45]. Both the atta-

Fig. 3 (a) Schematic of the trap sources that cause hysteresis in two-direction gate sweeps. (b) Transfer characteristics of a two-direction sweep

图 3 (a) 在双向扫描中引起回滞的缺陷态,(b) 双向扫描的转移特性曲线

ched molecules and the interface traps act as an adjustable capacitance in series with the channel region and gate dielectric, thus bringing a shift to the transfer curves. The magnitude of voltage shift corresponds to the amount of traps. As presented in Fig. 3 (b), the hysteresis width is 0.13 V at  $V_{\rm DS}=0.1$  V, and expands as 0.17 V at  $V_{\rm DS}=0.5$  V, where the device is measured in a dark chamber at 300 K, and the relative humidity is controlled under 30% [44]. The small hysteresis [16, 29, 43, 45] of our device indicates a mild influence induced by the trapformed 'capacitance'. The expand of the hysteresis window at  $V_{\rm DS}=0.5$  V might be jointly induced by the residual attachment from the 0.1 V test and an enhanced absorption of impurities in the 0.5 V test due to stronger electron current in MoS<sub>2</sub>.

To eliminate the impurities attached to  $MoS_2$  membrane, one can simply apply a negative voltage stress to the device, which would decrease the 'doping level' in  $MoS_2$ , therefore less polar molecules (water) or electrophilic molecules will keep sticking in the 2D  $MoS_2$  layers [43]. A dryer atmosphere [44] or a vacuum testing environment also works in decreasing the hysteresis. Vacuum annealing would remove the foreign matter more thoroughly [22]. However, as long as the  $MoS_2$  channel is ex-

posed to ambient, the device's performance will be severely suppressed. It is better to coat a passivation layer or high-reduction-potential molecules over the channel region [14, 16, 46].

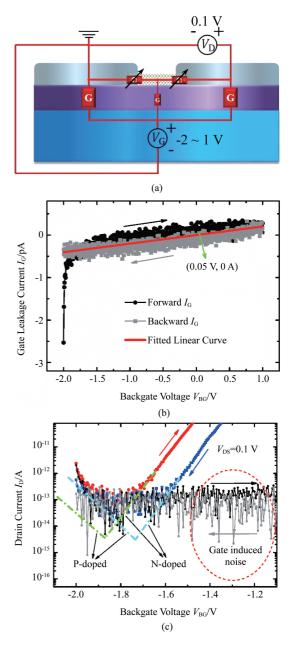

The gate induced drain noise (GIDN) was also taken into consideration. As shown in Fig. 4 (a), G stands for the conductance of each branch circuit. The adjustable resistances of the MoS, channel in Fig. 4 (a)

Fig. 4 (a) A simple circuit model of the gate leakage paths, (b) Gate leakage current in two sweep directions (black for forward and gray for backward) and the linear fitted curve, (c) Part of the drain current signal is swallowed by the gate induced noise at the off-state region

图 4 (a) 描述栅极漏电流的简单模型,(b) 两个方向扫描的栅极漏电(黑色代表正向,灰色代表反向),以及直线拟合电流,(c) 关断区域的部分漏极电流信号被栅致漏极噪声淹没

are the sums of the S/D contact resistances and the channel resistance. Most gate leakage in our device is induced by the overlap among two Al metal pads (70 µm ×70 µm) and the back gate. Considering the small area and high resistance of the MoS<sub>2</sub> sheet, the current between MoS<sub>2</sub> channel and back gate can be neglected. As displayed in Fig. 4 (b),  $I_D$  reaches ~  $10^{-12}$  A at the start points of the forward sweep. It is induced by a foreign pulse from the parasitic capacitance of the test system. Interestingly, a tiny hysteresis is also observed in the gate leakage of two directions, which could be a consequence of the altered tunneling conditions induced by trap movement in the SiO<sub>2</sub> layer<sup>[47]</sup>. However, the fitted linear curve calculated from the two-direction  $I_{\mathrm{BG}}$  current rightly goes through the point (0.05 V, 0 A), where  $I_{DG}$ (the branch current from drain to backgate) compensates  $I_{\rm SG}($  the branch current from backgate to source). It will help us to confirm the circuit model in Fig. 4(a) (assuming  $R_{\rm SG}$  =  $R_{\rm DG}$  ,  $R_{\rm SG}$  and  $R_{\rm DG}$  are the resistances between source/drain pad and backgate). Thus we can get a gate leakage density of 4. 12 nA/cm<sup>2</sup> under a  $2 \times 10^8$ V/m field, which suggests a good quality of the dielectric  $^{[18,\ 48-49]}$  . We can further get the GIDN  $(I_{\rm GIDN})$  by

$$I_{\text{GIDN}} = -I_{\text{BG}} - \frac{V_{\text{S}} - V_{\text{BG}}}{R_{\text{SG}}} = \frac{V_{\text{BG}}}{R_{\text{SG}}} - I_{\text{BG}} ,$$

(4)

$I_{\rm GIDN}$  in two directions are presented in Fig. 4 (c), and the extended dash lines present the  $I_{\rm D}$  signal of practical situation. The  $I_{\rm on}/I_{\rm off}$  ratio of our device is seemingly decreased by two orders. The gate leakage shrinks with less overlap area, thus the switch ratio will be further improved.

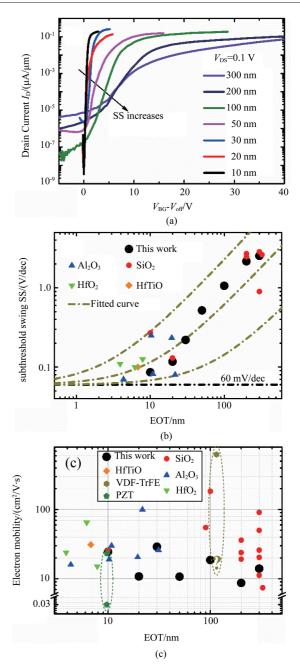

To further verify the influence of the dielectric thickness on the BG devices, devices with SiO<sub>2</sub> layers of different thicknesses were fabricated and characterized. The thicknesses of MoS<sub>2</sub> membranes vary from 5 nm to 35 nm. As presented in Fig. 5 (a), SS degrades with increasing SiO<sub>2</sub> thickness. To intuitively make a comparison among the transfer curves, all the curves are rearranged by properly setting the  $V_{\rm off}$  values. The extracted SS values from this work and other literatures ((  $SiO_2$  ) $^{[25,\ 26,\ 28-29,\ 50-51]}$ , (  $Al_2O_3$  ) $^{[7,\ 16,\ 52-54]}$ ,  $(HfO_2)^{[18,52,55]}$  and  $(HfTiO)^{[32]}$ ) are together displayed in Fig. 5 (b). All the devices included are BG Multi-layer (3  $\sim$  50 nm) MoS<sub>2</sub> FETs with their channel exposed to the ambient. In Fig. 5(b), three fitted curves are extracted from Eq. 2, where  $C_{\rm s}$  is assumed negligible and  $D_{\mbox{\tiny it}}$  values are set as  $3\times 10^{11}$  ,  $2\times 10^{12}$  and  $8\times 10^{12}$ cm<sup>-2</sup> • eV<sup>-1</sup>. Given Eq. 1 and the assumption that  $C_s$  is negligible, we can simply deduce that:

$SS \propto (1 + A \cdot D_{\rm it} \cdot T_{\rm OX})$  , (5) where  $T_{\rm OX}$  is the thickness of the SiO<sub>2</sub> layer, A is constant coefficient. Thus the SS of a BG MoS<sub>2</sub> FET is mainly determined by the interface trap density and EOT. During a wide  $D_{\rm it}$  range from  $3 \times 10^{11}$  to  $8 \times 10^{12}$  cm<sup>2</sup> · eV<sup>-1</sup>, a trend is observed in Fig. 5(b) that the SS value decreases when EOT becomes thinner. Interestingly, no obvious evidence is shown here that the  $D_{\rm it}$  of MoS<sub>2</sub>/SiO<sub>2</sub> interface is larger than that of MoS<sub>2</sub>/high- $\kappa$  dielectric in-

Fig. 5 (a) Transfer characteristics of BG ML-MoS $_2$  devices with different thickness of SiO $_2$  insulator, (b) SS as a function of EOT with different dielectric, (c) The mobility of BG MoS $_2$  devices with different dielectric

图 5 (a) 具有不同  $SiO_2$  介质厚度的背栅多层  $MoS_2$  器件的转移特性,(b) 亚阈值斜率与不同电介质的等效氧化层厚度(EOT)的关系,(c) 基于不同介质材料的背栅器件的迁移率

terface. Ref. [54] concludes that the distribution of  $D_{\rm it}$  and the peak of  $D_{\rm it}$  at native MoS<sub>2</sub> MOS interfaces are not strongly dependent on the gate dielectrics. Since the attached impurities will introduce a hysteresis to the BG devices, the  $D_{\rm it}$  calculated here is probably a sum of interface traps and channel attachments. Further studies should be developed to research the impact on SS brought by ambient impurities. In summary, the SS of a SiO<sub>2</sub>-

based BG device is possible to be properly shrunk.

Meanwhile, the mobility values of BG devices based on different dielectric have been displayed in Fig. 5(c), mobility values are from this work and Refs. [5, 13, 16, 18-19, 23, 28-29, 39, 50-51, 56] ( $SiO_2$ ), Refs. [7, 16, 52-54, 57] (Al<sub>2</sub>O<sub>2</sub>), Refs. [18, 52, 55](HfO<sub>2</sub>), Ref. [32](HfTiO), Ref. [58](VDF-TrFE)and Ref. [59] (PZT). All the mobility values are extracted through a two-probe test, using Eq. 3. No obvious relationship was observed between EOT and mobility. Surprisingly, the mobility values of BG MoS<sub>2</sub> FETs based on high-κ dielectric are not distinctly higher than those of SiO<sub>2</sub>-based devices, which is contrary to the previous results<sup>[18]</sup>. Generally, the contact resistance and the scattering rate are critical to a device's characteristics. Compared with the performance of devices based on low-κ dielectrics, a mobility of 184 cm<sup>2</sup>/V · s (SiO<sub>2</sub>) was reached by Ref. [19], owing to a rather small contact resistance and extremely low Schottky barrier. An average mobility of  $305 \text{ cm}^2/\text{V} \cdot \text{s} (\text{SiO}_2)$  was observed in Ref. [13], where a four-probe test system was applied, thus the negative influence of contact resistance was eliminated. Both results above present a promising outlook for SiO2-based MoS2 FETs. For devices characterized by a two-probe testing system, Y-function method is proved effectively in extracting the real field effect mobility  $^{[35]}$  . In the past works, the low tested mobilities of devices based on  $\mathrm{\bar{S}iO_2}$  are probably suppressed by high level of impurities and poor metal/MoS<sub>2</sub> contacts. As predicted in Ref. [20], MoS, devices based on low-κ dielectrics may perform better than those based on high-k dielectrics at room temperature, as long as the impurity level is reduced so that surface optical phonon scattering set the upper limit of carrier mobility.

In addition, devices with  $\mathrm{MoS}_2$  and ferroelectrics dielectrics have emerged recently. They have good potential in non-volatile memory and negative-capacitance transistors. The mobilitis versus different dielectrics (VDF-TrFE and PZT) are displayed in Fig. 5 (c). Due to the domain switching in ferroelectric membrane, memory windows are formed with transfer curves in two directions going anticlockwise [58-59], thus two maximum mobility values can be extracted within one device. As presented in Ref. [59], these two mobility values differ greatly due to the change of ferroelectric polarization direction. While Ref. [58] only presents the higher mobility value, leaving the smaller one unknown.

## 3 Conclusion

In summary, back-gated multi-layer  $MoS_2$  FETs based on different-thickness  $SiO_2$  substrates have been fabricated and characterized. With the  $SiO_2$  thickness scaling down to 10 nm, a minimum SS at 86 mV/dec has been achieved. As far as we know, it is the best SS value among the reported  $SiO_2$ -based BG devices. A mild hysteresis is observed in two direction sweeps, and it is mainly induced by the absorption/desorption process of impurities. The gate leakage of our device is very small, which suggests good electrical quality of the  $SiO_2$  layer.

When  $I_{\rm D}$  reaches ~  $10^{-13}$  A, the drain current signal is overwhelmed by GIDN, thus the switch ratio is underestimated. Smaller overlap area between Al pad and back gate will help to decrease GIDN. The SS and mobility are contrastively analyzed among the BG  ${\rm MoS}_2$  devices based on different oxide layers. Compared with  $D_{\rm it}$ , EOT shows a stronger influence on SS. More important, no evidence is observed that high- $\kappa$  dielectric is necessary in boosting the carrier mobility. The first thing before dielectric application in a  ${\rm MoS}_2$  FET is to consider the trade-off between impurity level and surface optical scattering. As discussed in this work, the  ${\rm MoS}_2/{\rm SiO}_2$  system shows undeveloped potentials for further exploration.

#### References

- [1] Ghatak S, Pal A N, Ghosh A. Nature of electronic states in atomically thin MoS, field-effect transistors [J]. Acs Nano, 2011, 5(10):7707.

- [2] Chen Min-Cheng, Lin Chia-Yi, Li Kai-Hsin, et al. Hybrid Si/TMD 2D electronic double channels fabricated using solid CVD few-layer-MoS2 stacking for V th matching and CMOS-compatible 3DFETs [C]. Electron Devices Meeting (IEDM), 2014 IEEE International 2014;33.5.1.

- [3] Desai S B, Madhvapathy S R, Sachid A B, et al. MoS<sub>2</sub> transistors with 1-nanometer gate lengths [J]. Science, 2016, 354(6308):99.

- [4] Jin K, Xie L M, Tian Y, et al. Au-Modified Monolayer MoS<sub>2</sub> Sensor for DNA Detection [J]. Journal of Physical Chemistry C, 2016, 120 (20):11204.

- [5] Ye Lei, Li Hao, Chen Zefeng, et al. Near-infrared photodetector based on MoS<sub>2</sub>/black phosphorus heterojunction [J]. ACS Photonics, 2016, 3(4):692-699.

- [6] Pu Jiang, Yomogida Y, Liu Keng-Ku, et al. Highly flexible MoS2 thin-film transistors with ion gel dielectrics [J]. Nano Lett, 2012, 12 (8):4013.

- [7] Salvatore G A, Munzenrieder N, Barraud C, et al. Fabrication and transfer of flexible few-layers MoS<sub>2</sub> thin film transistors to any arbitrary substrate [J]. Acs Nano, 2013, 7(10):8809.

- [8] Radisavljevic B, Radenovic A, Brivio J, et al. Single-layer MoS<sub>2</sub> transistors [J]. Nat Nanotechnol, 2011, 6(3):147.

- [9] Das S, Appenzeller J. Screening and interlayer coupling in multilayer MoS<sub>2</sub>[J]. Physica Status Solidi-Rapid Research Letters, 2013, 7(4): 268

- [10] Jena D, Konar A. Enhancement of carrier mobility in semiconductor nanostructures by dielectric engineering [J]. Phys Rev Lett, 2007, 98 (13):136805.

- [11] Splendiani A, Sun Liang, Zhang Yuan-Bo, et al. Emerging photoluminescence in monolayer MoS<sub>2</sub>[J]. Nano Lett, 2010, 10(4):1271.

- [12] Jariwala D, Sangwan V K, Late D J, et al. Band-like transport in high mobility unencapsulated single-layer MoS<sub>2</sub> transistors [ J ]. Applied Physics Letters, 2013, 102(17):173107.

- [13] Pradhan N R, Rhodes D, Zhang Q, et al. Intrinsic carrier mobility of multi-layered MoS<sub>2</sub> field-effect transistors on SiO<sub>2</sub>[J]. Applied Physics Letters, 2013, 102(12):123105.

- [14] Min S-W, Lee H S, Choi H J, et al. Nanosheet thickness-modulated MoS<sub>2</sub> dielectric property evidenced by field-effect transistor performance [J]. Nanoscale, 2013, 5(2):548.

- [15] Radisavljevic B, Radenovic A, Brivio J, et al. Single-Layer MoS<sub>2</sub> Transistors [J]. Nat. Nanotechnol, 2011, 6:147.

- [16] Li Tao, Wan Ben-Song, Du Gang, et al. Electrical performance of multilayer MoS<sub>2</sub> transistors on high-k Al<sub>2</sub>O<sub>3</sub> coated Si substrates [J]. AIP Advances, 2015, 5(5):057102.

- [ 17 ] Bao Wen-Zhong, Cai Xing-Han, Kim D, et al. High mobility ambipolar MoS<sub>2</sub> field-effect transistors; Substrate and dielectric effects [ J ]. Applied Physics Letters, 2013, 102(4):042104.

- [18] Ganapathi K L, Bhattacharjee S, Mohan S, et al. High-Performance

- $HfO_2$  Back Gated Multilayer  $MoS_2$  Transistors [J]. *IEEE Electron Device Letters*, 2016, 37(6):797.

- [19] Das S, Chen Hong-Yan, Penumatcha A V, et al. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts [J]. Nano Lett, 2013, 13(1):100.

- [20] Ma Nan, Jena D. Charge Scattering and Mobility in Atomically Thin Semiconductors [J]. Physical Review X, 2014, 4(1):011043.

- [21] Wang Feng-Lin, Stepanov P, Gray M, et al. Annealing and transport studies of suspended molybdenum disulfide devices [J]. Nanotechnology, 2015, 26(10):105709.

- [22] Qiu Hao, Pan Li-Jia, Yao Zong-Ni, et al. Electrical characterization of back-gated bi-layer MoS<sub>2</sub> field-effect transistors and the effect of ambient on their performances [J]. Applied Physics Letters, 2012, 100 (12):123104.

- [23] Yang S, Park S, Jang S, et al. Electrical stability of multilayer MoS<sub>2</sub> field effect transistor under negative bias stress at various temperatures [J]. Physica Status Solidi (RRL)-Rapid Research Letters, 2014, 8(8):714.

- [24] Wu Wei, De D, Chang Su-Chi, et al. High mobility and high on/off ratio field-effect transistors based on chemical vapor deposited singlecrystal MoS<sub>2</sub> grains [J]. Applied Physics Letters, 2013, 102 (14): 142106.

- [25] Das S, Appenzeller J. Evaluating the scalability of multilayer MoS<sub>2</sub> transistors [C]. Device Research Conference (DRC), 2013 71st Annual 2013:153.

- [26] Yuan Hui, Cheng Guang-Jun, You Lin, et al. Influence of metal MoS2 interface on MoS2 transistor performance; Comparison of Ag and Ti contacts [J]. ACS applied materials & interfaces, 2015, 7(2): 1180.

- [27] Ly T H, Perello D J, Zhao Jiong, et al. Misorientation-angle-dependent electrical transport across molybdenum disulfide grain boundaries [J]. Nat Commun, 2016, 7:10426.

- [28] Yoo G, Lee S, Yoo B, et al. Electrical contact analysis of multilayer MoS<sub>2</sub> transistor with molybdenum source/drain electrodes [J]. IEEE Electron Device Letters, 2015, 36(11):1215.

- [29] Park Y, Baac H W, Heo J, et al. Thermally activated trap charges responsible for hysteresis in multilayer MoS<sub>2</sub> field-effect transistors [J]. Applied Physics Letters, 2016, 108(8):083102.

- [30] Kolla L. G., Bhattacharjee S., S. M., et al. High Performance Hf02 Back Gated Multilayer MoS<sub>2</sub> transistors [J]. *IEEE Electron Device Letters*,

- [31] Sze S M, Ng K K. Physics of semiconductor devices [M]. John wiley & sons, 2006.

- [ 32 ] Wen Ming, Xu Jing-Ping, Liu Lu, et al. Improved Electrical Performance of Multilayer MoS<sub>2</sub> Transistor With NH 3-Annealed ALD HfTiO Gate Dielectric [ J ]. IEEE Transactions on Electron Devices, 2017, 64 (3):1020.

- [33] Cheng Zhi-Hui, Cardenas J A, McGuire F, et al. Modifying the Ni-MoS<sub>2</sub> Contact Interface Using a Broad-Beam Ion Source [J]. IEEE Electron Device Letters, 2016, 37(9):1234.

- [34] Ghibaudo G. New method for the extraction of MOSFET parameters

[J]. Electronics Letters, 1988, 24(9):543.

- [35] Na Jun-Hong, Shin M, Joo M K, et al. Separation of interlayer resistance in multilayer MoS<sub>2</sub> field-effect transistors [J]. Applied Physics Letters, 2014, 104(23):233502.

- [36] Lee H S, Min S W, Chang Y G, et al. MoS<sub>2</sub> Nanosheet Phototransistors with Thickness-Modulated Optical Energy Gap [J]. Nano Letters, 2012, 12(7):3695.

- [37] Esmaeili-Rad M R, Salahuddin S. High performance molybdenum disulfide amorphous silicon heterojunction photodetector [J]. Sci Rep, 2013, 3:2345.

- [38] Yoon J, Park W, Bae G Y, et al. Highly flexible and transparent multilayer MoS<sub>2</sub> transistors with graphene electrodes [J]. Small, 2013, 9 (19):3295

- [39] Liu Wei, Kang Jia-Hao, Cao Wei, et al. High-performance few-layer-

- MoS<sub>2</sub> field-effect-transistor with record low contact-resistance [C]. *Electron Devices Meeting (IEDM)*, 2013 IEEE International 2013;19.4.1.

- [40] Joo M K, Moon B H, Ji H, et al. Electron Excess Doping and Effective Schottky Barrier Reduction on the MoS<sub>2</sub>/h-BN Heterostructure [J]. Nano Lett, 2016, 16(10):6383.

- [41] English C D, Shine G, Dorgan V E, et al. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-High Vacuum Metal Deposition [J]. Nano Lett, 2016, 16(6):3824.

- [42] Cheng Zhi-Hui, Cardenas J A, McGuire F, et al. Using Ar Ion beam exposure to improve contact resistance in MoS<sub>2</sub> FETs [C]. Device Research Conference (DRC), 2016 74th Annual 2016;1.

- [43] Late D J, Liu Bin, Matte H S, et al. Hysteresis in single-layer MoS<sub>2</sub> field effect transistors [J]. Acs Nano, 2012, 6(6):5635.

- [44] Li Tao, Du Gang, Zhang Bao-Shun, et al. Scaling behavior of hysteresis in multilayer MoS<sub>2</sub> field effect transistors [J]. Applied Physics Letters, 2014, 105(9):093107.

- [45] Cho K, Park W, Park J, et al. Electric stress-induced threshold voltage instability of multilayer MoS<sub>2</sub> field effect transistors [J]. Acs Nano, 2013, 7(9):7751.

- [46] Kiriya D, Tosun M, Zhao Pei-Da, et al. Air-Stable Surface Charge Transfer Doping of MoS<sub>2</sub> by Benzyl Viologen [J]. Journal of the American Chemical Society, 2014, 136(22):7853.

- [47] Houssa M, Tuominen M, Naili M, et al. Trap-assisted tunneling in high permittivity gate dielectric stacks [J]. Journal of Applied Physics, 2000, 87 (12):8615.

- [48] Yang Wen, Sun Qing-Qing, Geng Yang, et al. The Integration of Sub-10 nm Gate Oxide on MoS<sub>2</sub> with Ultra Low Leakage and Enhanced Mobility [J]. Sci Rep., 2015, 5:11921.

- [49] Wang Xiao, Zhang Tian-Bo, Yang Wen, et al. Improved integration of ultra-thin high-k dielectrics in few-layer MoS<sub>2</sub> FET by remote forming gas plasma pretreatment [J]. Applied Physics Letters, 2017, 110 (5):053110.

- [50] Kwon H-J, Jang J, Kim S, et al. Electrical characteristics of multilayer MoS<sub>2</sub> transistors at real operating temperatures with different ambient conditions [J]. Applied Physics Letters, 2014, 105 (15):152105.

- [51] Roh J, Lee J-H, Jin S H, et al. Negligible hysteresis of molybdenum disulfide field-effect transistors through thermal annealing [J]. Journal of Information Display, 2016, 17(3):103.

- [52] Chang H Y, Yang Shi-Xuan, Lee J, et al. High-performance, highly bendable MoS2 transistors with high-k dielectrics for flexible low-power systems [J]. Acs Nano, 2013, 7(6):5446.

- [53] Kim S, Konar A, Hwang W S, et al. High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals [J]. Nat Commun, 2012, 3:1011.

- [54] Takenaka M, Ozawa Y, Han J, et al. Quantitative evaluation of energy distribution of interface trap density at MoS<sub>2</sub> MOS interfaces by the Terman method [C]. Electron Devices Meeting (IEDM), 2016 IEEE International 2016:5.8. 1.

- [55] Wen Ming, Xu Jing-Ping, Liu Lu, et al. Effects of annealing on electrical performance of multilayer MoS<sub>2</sub> transistors with atomic layer deposited HfO<sub>2</sub> gate dielectric [J]. Applied Physics Express, 2016, 9 (9).095202.

- [56] Arora H, Seifert G, Cuniberti G, et al. Electrical characterization of two-dimensional materials and their heterostructures [C]. Radio and Antenna Days of the Indian Ocean (RADIO), 2016 IEEE 2016;1.

- [57] Kang Jia-Hao, Liu Wei, Banerjee K. High-performance MoS2 transistors with low-resistance molybdenum contacts [J]. Applied Physics Letters, 2014, 104(9):093106.

- [58] Kobayashi T, Hori N, Nakajima T, et al. Electrical characteristics of MoS<sub>2</sub> field-effect transistor with ferroelectric vinylidene fluoride-trifluoroethylene copolymer gate structure [J]. Applied Physics Letters, 2016. 108 (13):132903.

- [59] Ko C, Lee Y, Chen Ya-Bin, et al. Ferroelectrically Gated Atomically Thin Transition-Metal Dichalcogenides as Nonvolatile Memory[J]. Advanced Materials, 2016.